### CSE211: Compiler Design Oct. 18, 2021

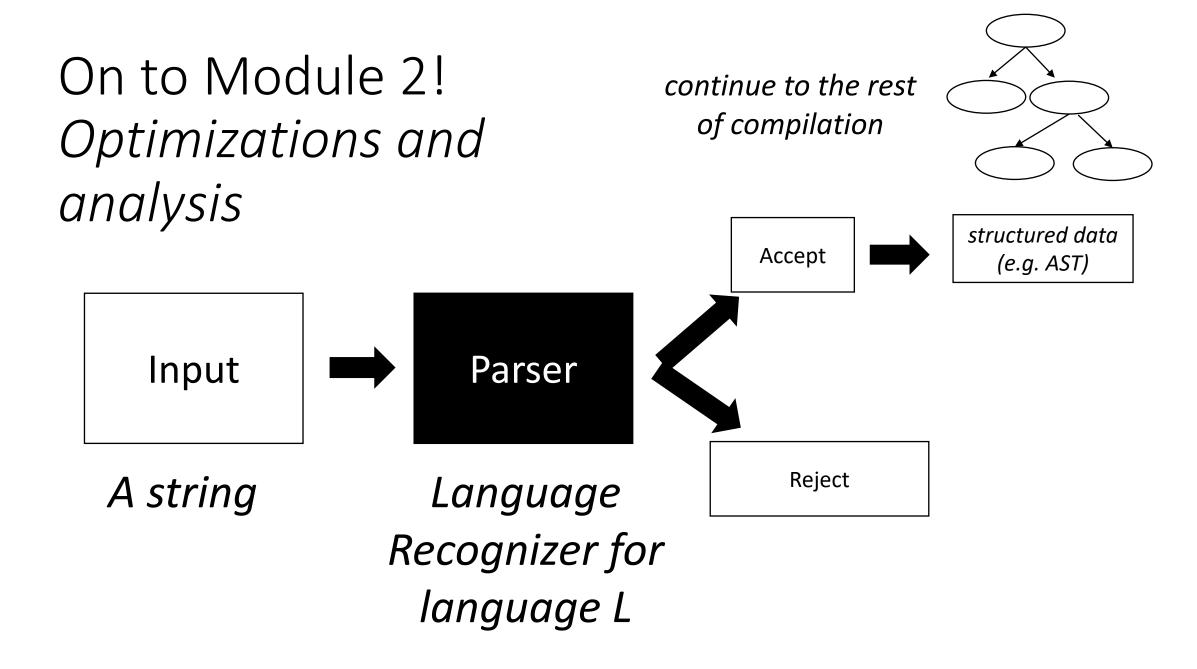

- **Topic**: Introduction to Module 2: analysis and optimizations!

- Questions:

- What sort of compiler optimizations do you know about?

- What sort of intermediate representations do you know about?

### Announcements

- Homework 1 is out

- Due on the 25<sup>th</sup>

- One week!

- No extensions

- Get your paper reading approved by me by Monday

- No extensions, 5% of your grade

- One more office hour:

- Thursday 3 5 PM

#### Announcements

- I will be gone Monday and Wednesday next week to attend a khronos group meeting.

- The schedule is still in flux:

- either I will hold class synchronously on Zoom

- Or provide asynchronous lectures

- Maybe a combination, stay tuned

### Intermediate representations (IRs)

- Intermediate step between human-accessible programming languages and horrible machine ISAs

- Ideal for analysis because:

- More regularity than high-level languages (simple instructions)

- Less constraints than ISA languages (virtual registers)

- Machine-agnostic optimizations

- See Godbolt example

# Different IRs

Many different IRs, each have different purposes

- Trees

- Abstract syntax trees

- Data-dependency trees

- Good for instruction scheduling

- Textual

- 3 address code

- Good for removing redundant expressions

- Graphs

- Control flow graphs

- Good for data flow analysis (finding uninitialized variables)

# Different IRs

Many different IRs, each have different purposes

- Trees

- Abstract syntax trees

- Data-dependency trees

- Good for instruction scheduling

- Textual

- 3 address code

- Good for removing redundant expressions

- Graphs

- Control flow graphs

- Good for data flow analysis (finding uninitialized variables)

What are some examples of a modern compiler pipeline?

GPUs often have many IRs... why?

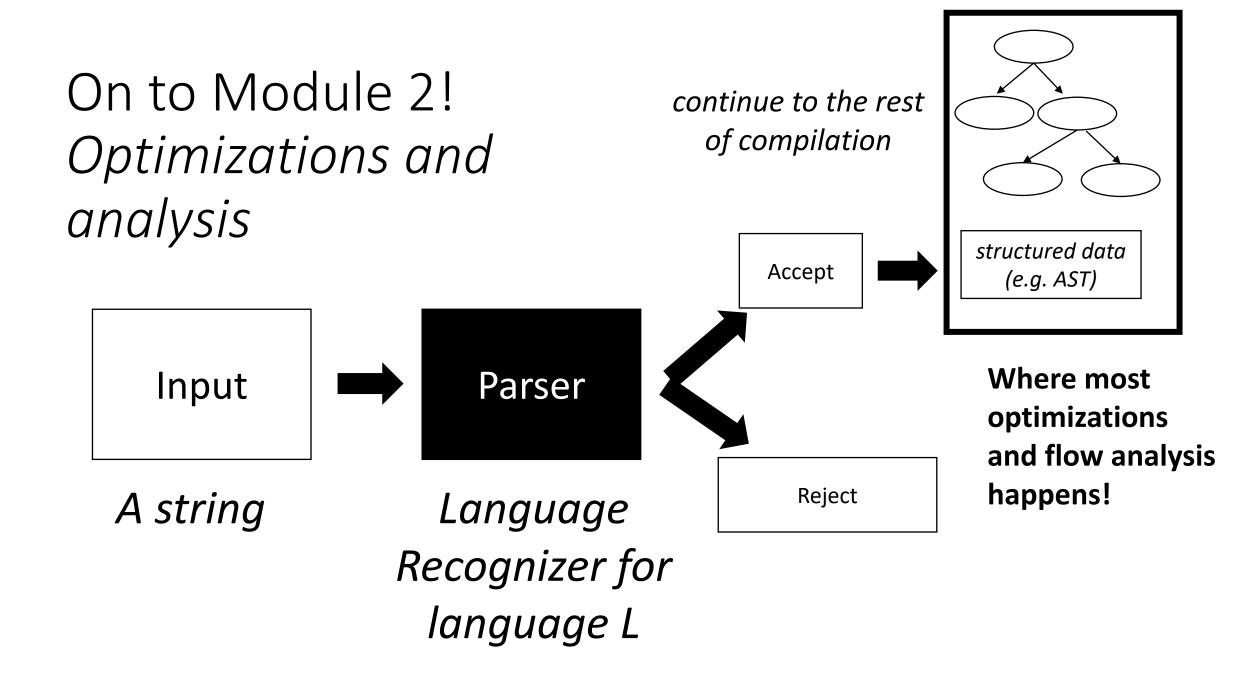

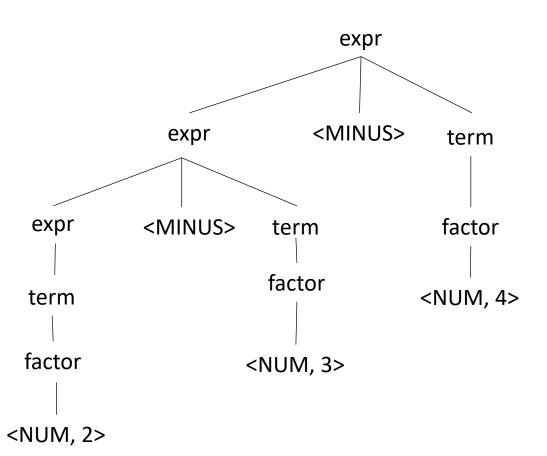

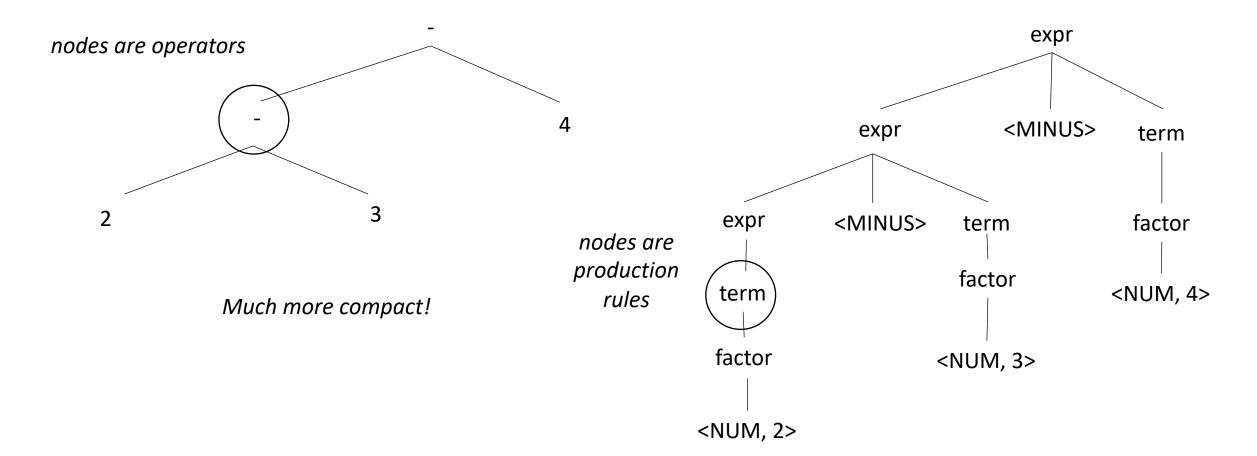

• Remember the expression parse tree

Operator Name **Productions** : expr PLUS term +,expr expr MINUS term term \*,/ : term TIMES pow term term DIV pow Pow : factor CARROT pow Λ pow factor () : LPAR expr RPAR factor | NUM

input: 2-3-4

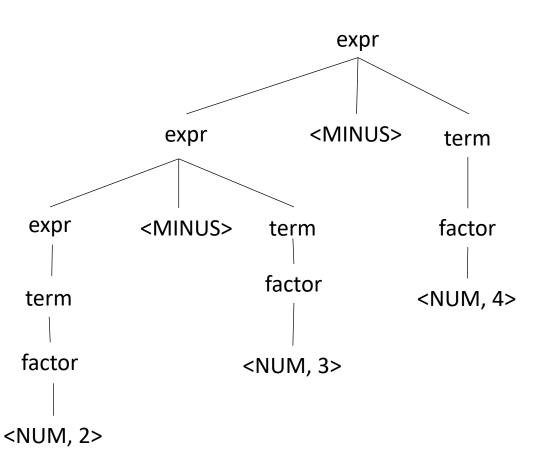

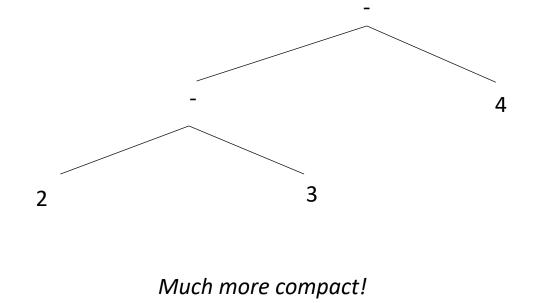

• Convert into an AST

#### input: 2-3-4

• Convert into an AST

input: 2-3-4

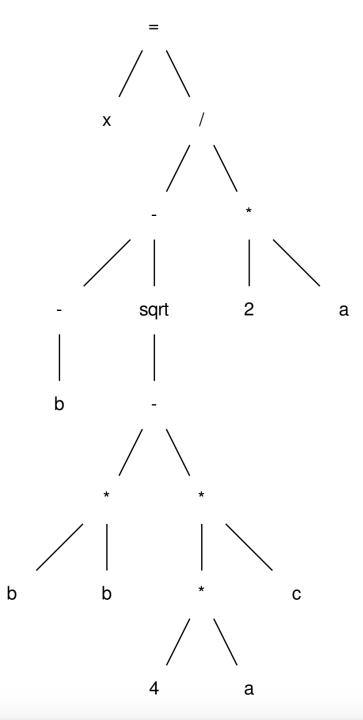

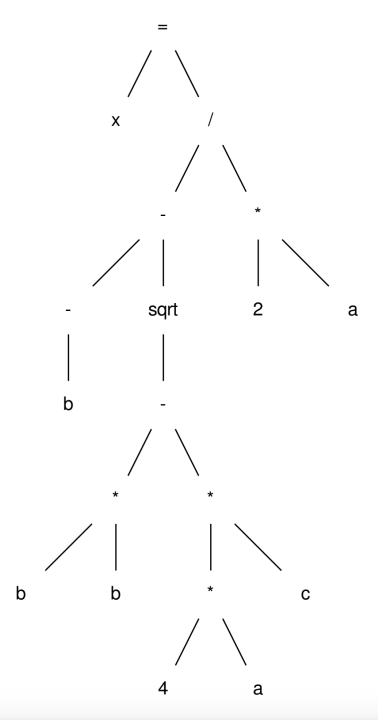

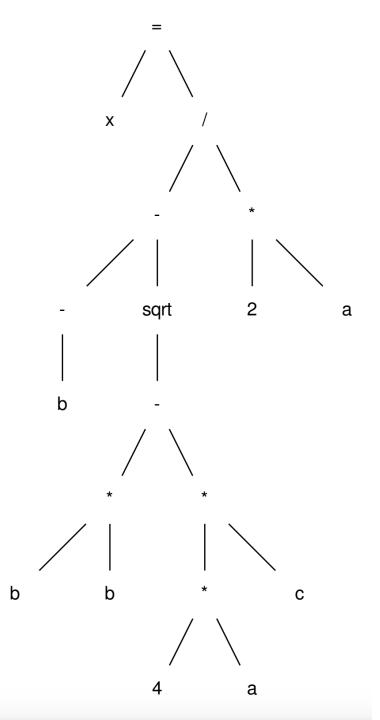

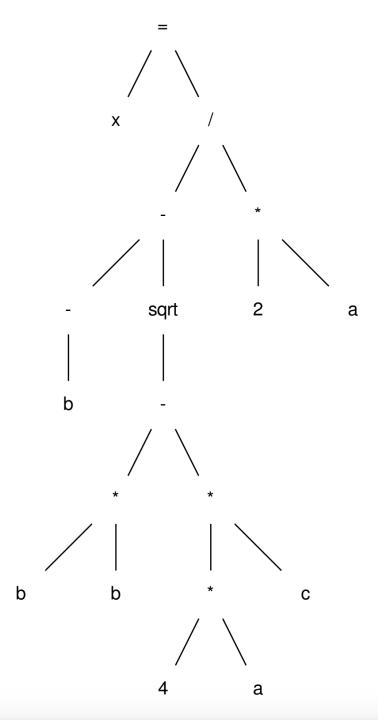

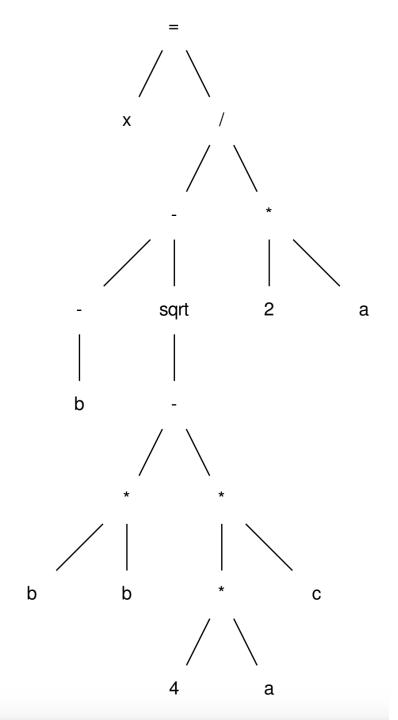

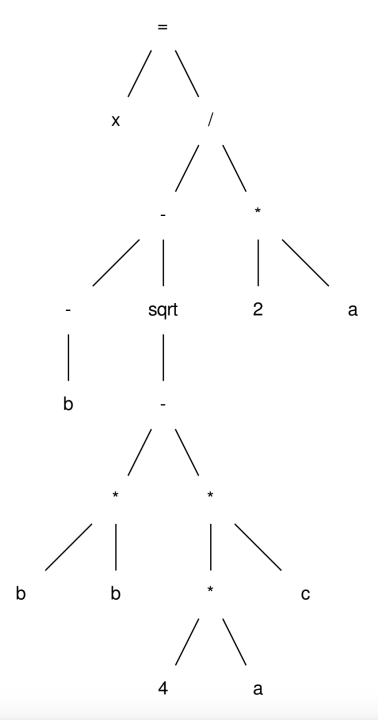

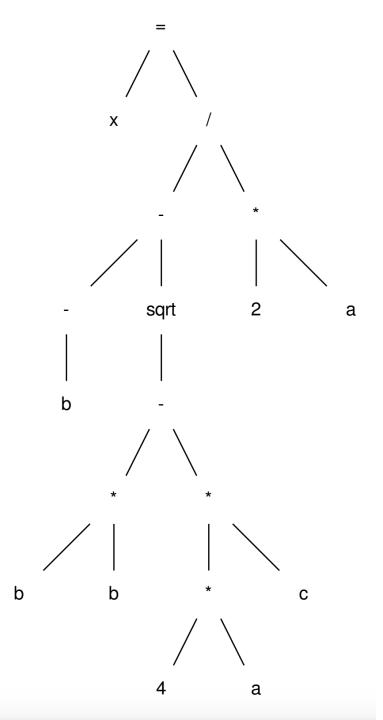

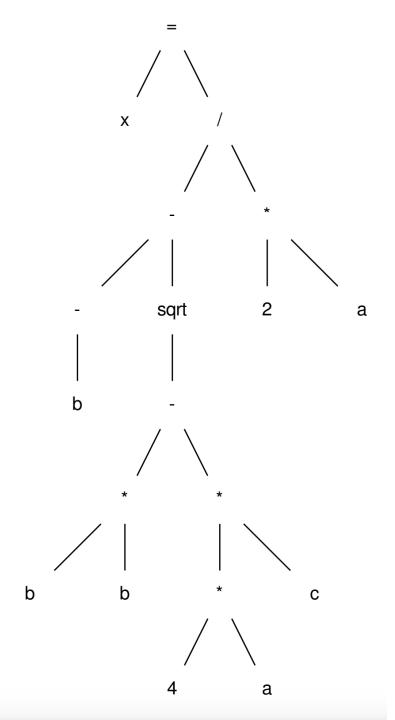

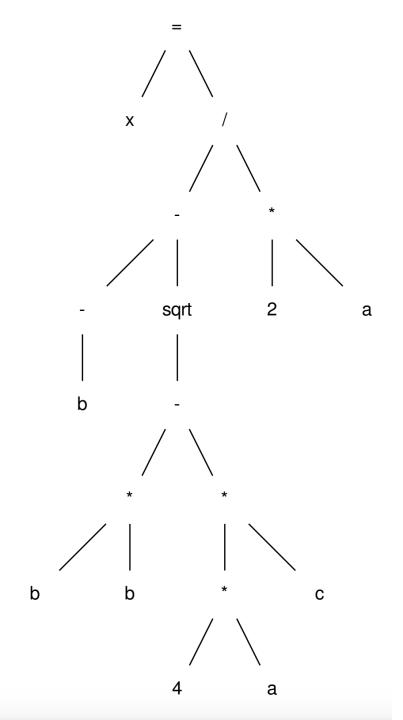

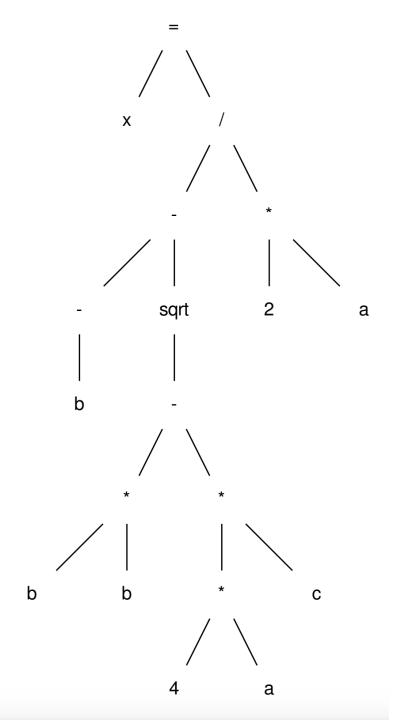

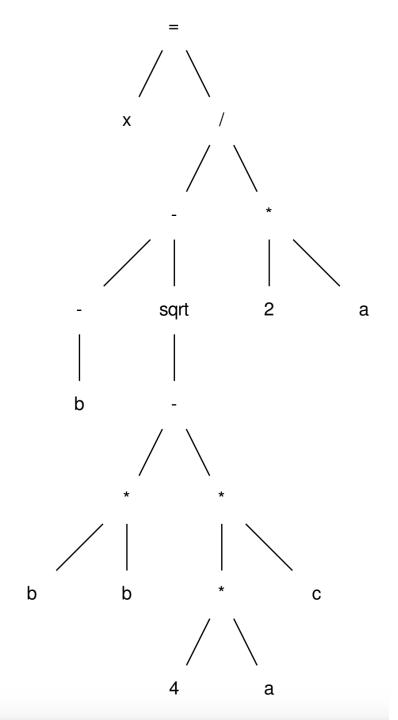

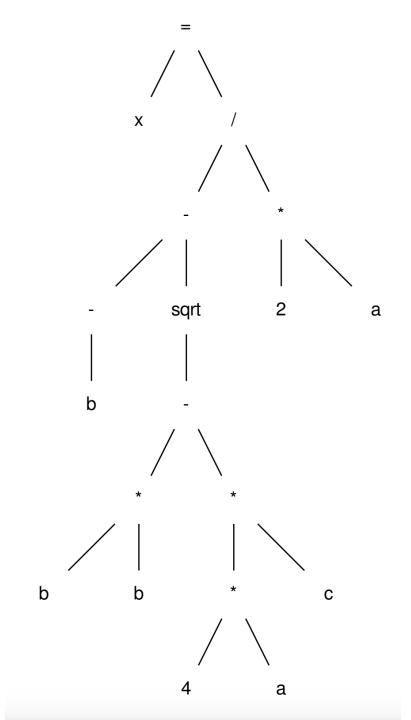

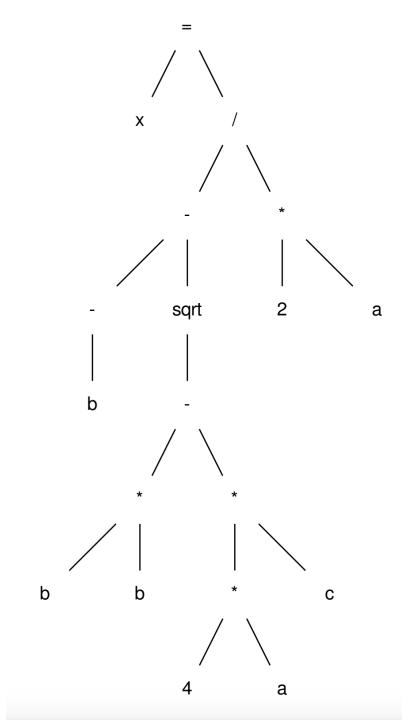

• Easier to see bigger trees, e.g. quadratic formula:

$$x = \frac{-b \pm \sqrt{b^2 - 4ac}}{2a}$$

$$x = (-b - sqrt(b*b - 4 * a * c)) / (2*a)$$

Thanks to Sreepathi Pai for the example!

$$x = (-b - sqrt(b*b - 4 * a * c)) / (2*a)$$

- Each instruction consists of 3 "addresses"

- Address here means a virtual register or value

- unlimited virtual registers

- represented many ways:

rx = ry op rz;

r5 = r3 + r6; r6 = r0 \* r7;

- Each instruction consists of 3 "addresses"

- Address here means a virtual register or value

- unlimited virtual registers

- represented many ways:

rx←ry op rz;

r5←r3 + r6; r6←r0 \* r7;

- Each instruction consists of 3 "addresses"

- Address here means a virtual register or value

- unlimited virtual registers

- represented many ways:

rx = **op** ry, rz;

r5 = add r3, r6; r6 = mult r0, r7;

- Each instruction consists of 3 "addresses"

- Address here means a virtual register or value

- unlimited virtual registers

- some instructions don't fit the pattern:

store ry, rz;

r5 = copy r3; r6 = call(r0, r1, r2, r3...);

- Each instruction consists of 3 "addresses"

- Address here means a virtual register or value

- unlimited virtual registers

- Other information:

- Annotated

- Typed

- Alignment

r5 = r3 + r6; !dbg !22 r6 = r0 \*(int32) 67; store(r1,r2), aligned 8

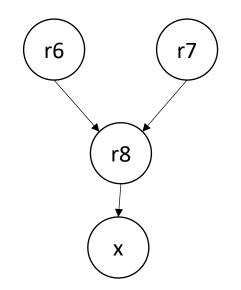

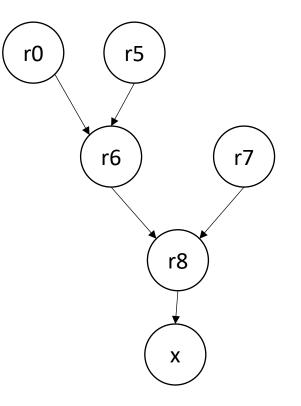

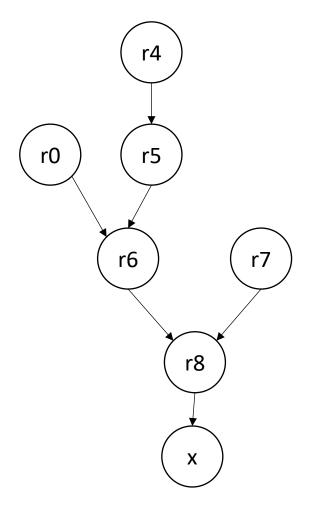

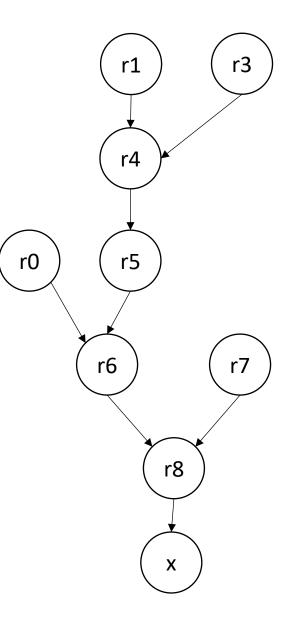

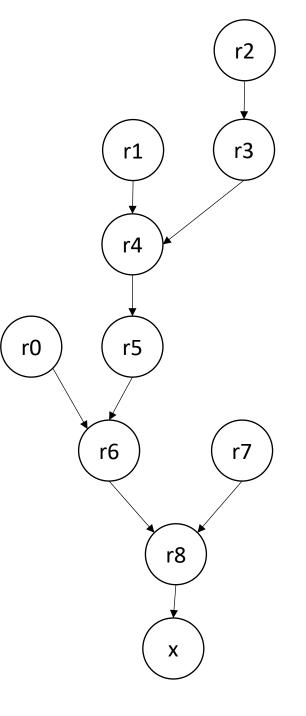

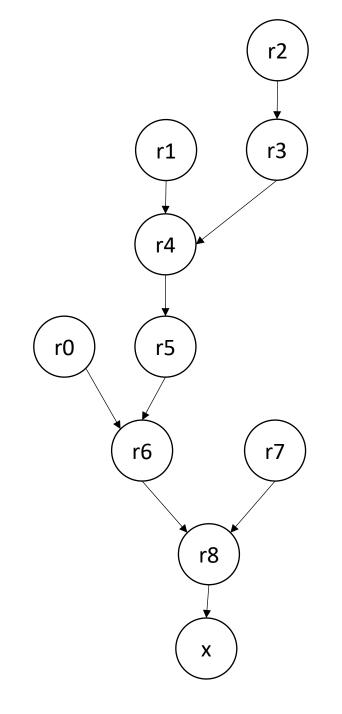

post-order traversal, creating virtual registers for each node

r0 = neg(b);

post-order traversal, creating virtual registers for each node

r0 = neg(b); r1 = b \* b;

post-order traversal, creating virtual registers for each node

r0 = neg(b); r1 = b \* b; r2 = 4 \* a;

post-order traversal, creating virtual registers for each node

r0 = neg(b); r1 = b \* b; r2 = 4 \* a; r3 = r2 \* c; r4 = r1 - r3; r5 = sqrt(r4); r6 = r0 - r5;

post-order traversal, creating virtual registers for each node

r0 = neg(b); r1 = b \* b; r2 = 4 \* a; r3 = r2 \* c; r4 = r1 - r3; r5 = sqrt(r4); r6 = r0 - r5; r7 = 2 \* a;

post-order traversal, creating virtual registers for each node

post-order traversal, creating virtual registers for each node

post-order traversal, creating virtual registers for each node

r0 = neg(b);r1 = b \* b; r2 = 4 \* a;r3 = r2 \* c;r4 = r1 - r3;r5 = sqrt(r4);r6 = r0 - r5;r7 = 2 \* a;r8 = r6 / r7; x = r8;

This is the similar code we'd see in LLVM! See Godbolt example

#### What now?

We can more easily compile to machine code **OR**

```

r0 = neg(b);

r1 = b * b;

r2 = 4 * a;

r3 = r2 * c;

r4 = r1 - r3;

r5 = sqrt(r4);

r6 = r0 - r5;

r7 = 2 * a;

r8 = r6 / r7;

x = r8;

```

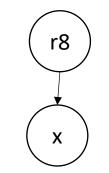

What now?

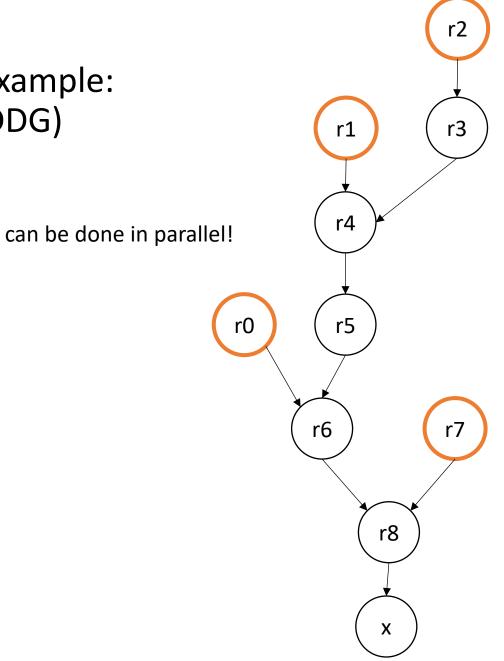

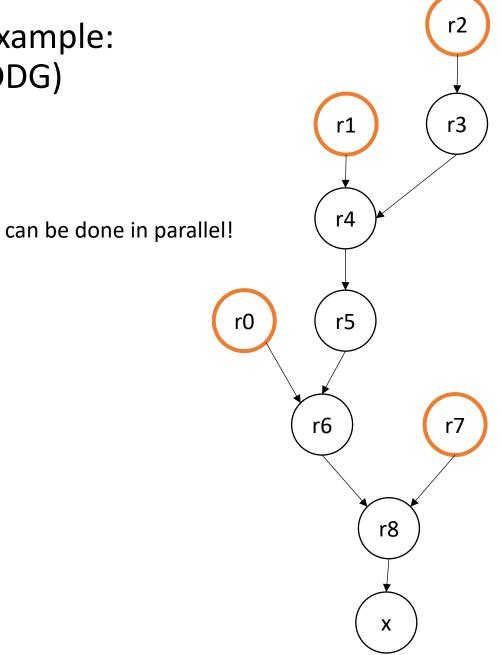

We can perform more optimizations, example: by making a data-dependency graph (DDG)

What can this tell us?

r0 = neq(b);r1 = b \* b; r2 = 4 \* a;r3 = r2 \* c;r4 = r1 - r3;r5 = sqrt(r4);r6 = r0 - r5;r7 = 2 \* a; r8 = r6 / r7; x = r8;

Can be hoisted!

r0 = neq(b);r1 = b \* b; r2 = 4 \* a; r3 = r2 \* c;should we hoist this one? r4 = r1 - r3;r5 = sqrt(r4);r6 = r0 - r5;r7 = 2 \* a;r8 = r6 / r7; x = r8;

r2 r3 r1 r4 r5 r0 r6 r7 r8 Х

# Lots of considerations in optimizing

- More on instruction scheduling later

- Processor agnostic?

- Back to 3-address code

- We looked at expressions, but how about conditionals?

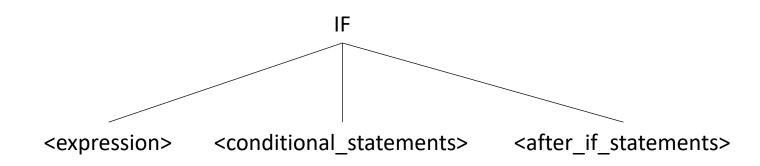

• 3 address code typically contains a conditional branch:

br <reg>, <label0>, <label1>

if the value in <reg> is true, branch to <label0>, else branch to <label1>

br <label0>

unconditional branch

if (expr) {

// conditional statements

}

// after if statements

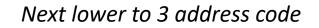

First, produce an AST

if (expr) {

// conditional statements

}

// after if statements

```

if (expr) {

// conditional statements

}

// after if statements

```

```

after_if:

<after if statements>;

```

```

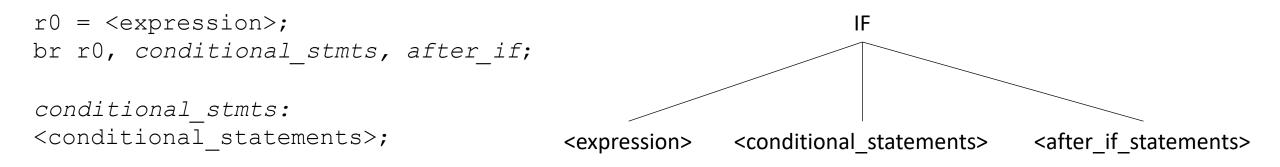

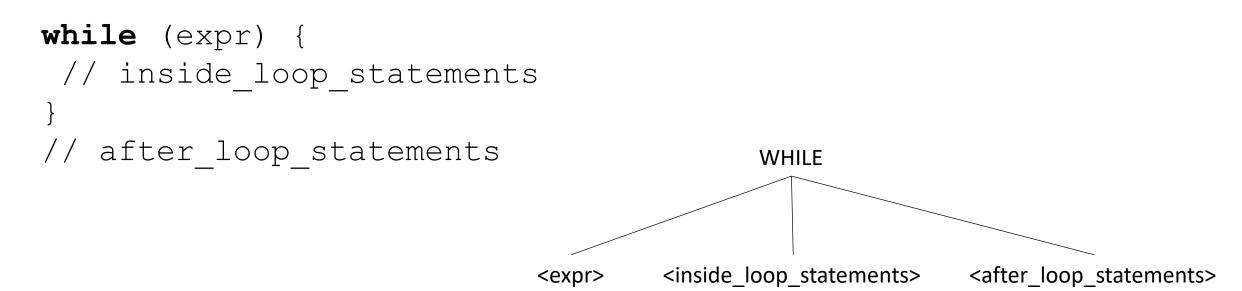

while (expr) {

// inside_loop_statements

}

// after_loop_statements

```

```

while (expr) {

// inside_loop_statements

}

// after_loop_statements

```

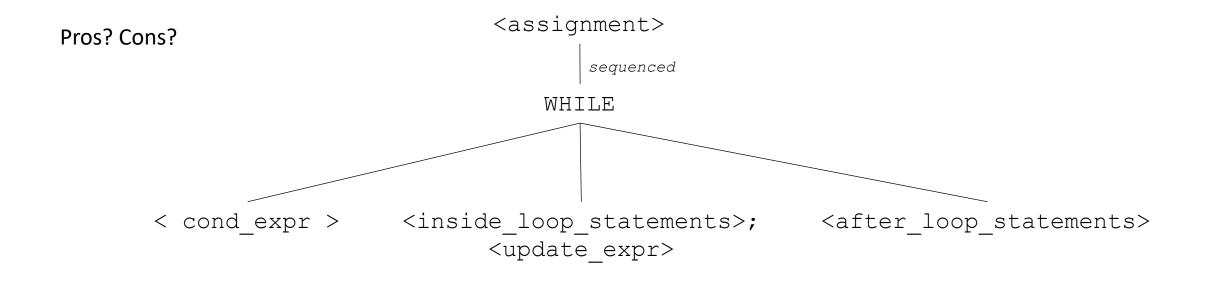

First, produce an AST

```

while (expr) {

// inside loop statements

// after loop statements

WHILE

beginning label:

r0 = \langle expr \rangle

<inside_loop_statements>

<after_loop_statements>

<expr>

br r0, inside loop, after loop;

inside loop:

<inside loop statements>

br beginning label;

after loop:

<after loop_statements>

```

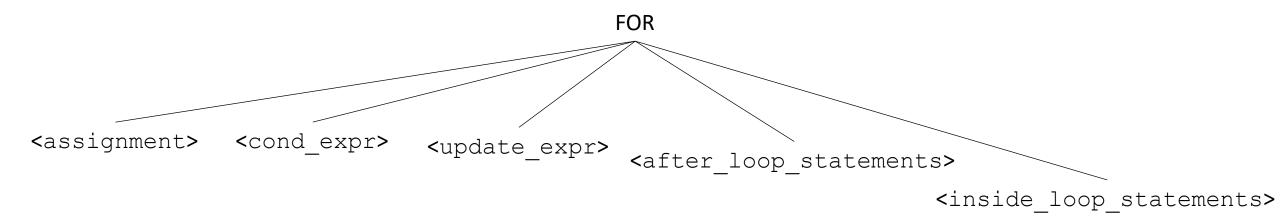

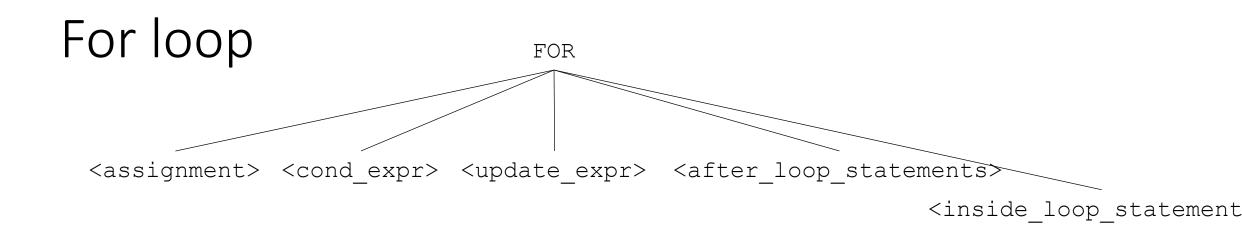

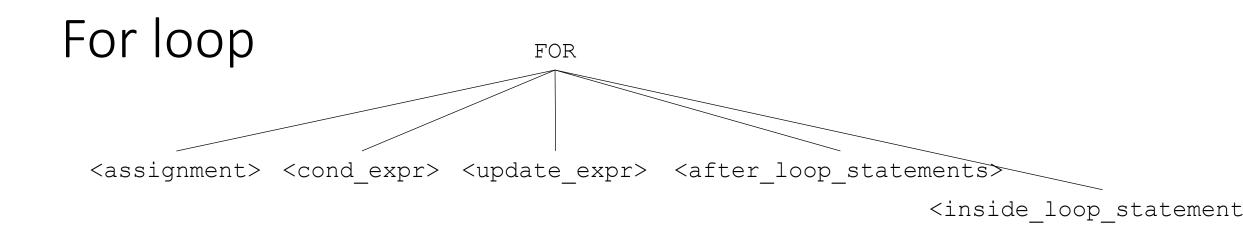

### For loop

for (assignment; cond\_expr; update\_expr) {

// inside\_loop\_statements

}

// after loop\_statements

### For loop

for (assignment; cond\_expr; update\_expr) {

// inside\_loop\_statements

}

// after\_loop\_statements

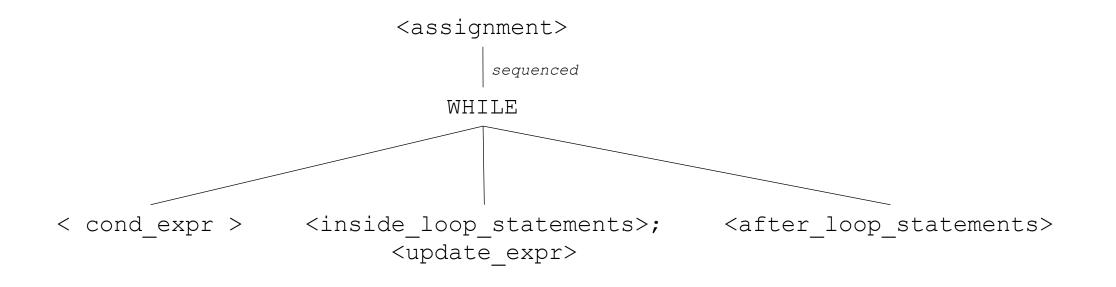

Can be de-sugared into a while loop:

Can be de-sugared into a while loop:

- A sequence of 3 address instructions

- Programs can be split into **Basic Blocks**:

- A sequence of 3 address instructions such that:

- There is a single entry, single exit

• *Important property*: an instruction in a basic block can assume that all preceding instructions will execute

#### Single Basic Block

- A sequence of 3 address instructions

- Programs can be split into **Basic Blocks**:

- A sequence of 3 address instructions such that:

- There is a single entry, single exit

• *Important property*: an instruction in a basic block can assume that all preceding instructions will execute

Single Basic Block Label x: op1; op2; op3; br label z;

**Two Basic Blocks**

```

Label_x:

op1;

op2;

op3;

Label_y:

op4;

op5;

```

How might they appear in a high-level language? What are some examples?

- A sequence of 3 address instructions

- Programs can be split into **Basic Blocks**:

- A sequence of 3 address instructions such that:

- There is a single entry, single exit

• *Important property*: an instruction in a basic block can assume that all preceding instructions will execute

Single Basic Block Label x: op1; op2; op3; br label z;

#### **Two Basic Blocks**

Label x:

Label y:

op1;

op2;

op3;

op4;

op5;

- A sequence of 3 address instructions

- Programs can be split into **Basic Blocks**:

- A sequence of 3 address instructions such that:

- There is a single entry, single exit

• *Important property*: an instruction in a basic block can assume that all preceding instructions will execute How might they appear in a high-level language?

Four Basic Blocks

**Two Basic Blocks**

Single Basic Block

Label\_x:

Label\_x:

op1;

op1;

op2;

op3;

Label\_y:

br label\_z;

op4;

op5;

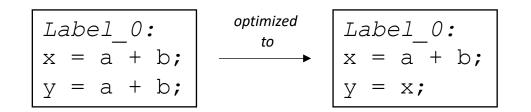

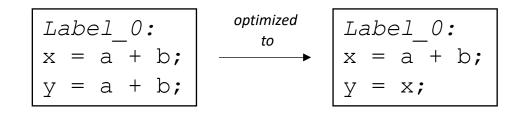

#### • Local optimizations:

• Optimizes an individual basic block

### • Regional optimizations:

• Combines several basic blocks

### Global optimizations:

- operates across an entire procedure

- what about across procedures?

- Local optimizations:

- Optimizes an individual basic block

#### • Regional optimizations:

Combines several basic blocks

### Global optimizations:

- operates across an entire procedure

- what about across procedures?

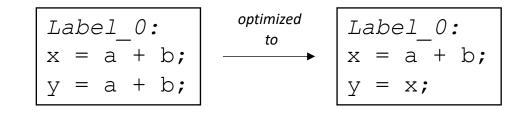

Label\_0: x = a + b; y = a + b;

- Local optimizations:

- Optimizes an individual basic block

#### • Regional optimizations:

Combines several basic blocks

### Global optimizations:

- operates across an entire procedure

- what about across procedures?

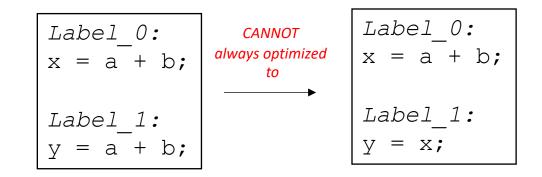

- Local optimizations:

- Optimizes an individual basic block

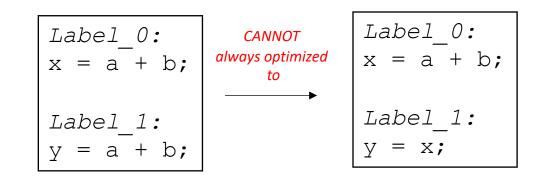

- Regional optimizations:

- Combines several basic blocks

### Global optimizations:

- operates across an entire procedure

- what about across procedures?

- Local optimizations:

- Optimizes an individual basic block

- Regional optimizations:

- Combines several basic blocks

- Global optimizations:

- operates across an entire procedure

- what about across procedures?

code could skip Label\_0, leaving x undefined!

# **Regional Optimization**

| …<br>if (x) {   |  |

|-----------------|--|

| <br>}<br>else { |  |

| x = a + b;<br>} |  |

| y = a + b;<br>  |  |

at a higher-level, we cannot replace: y = a + b. with y = x;

# **Regional Optimization**

| <br>  if | - | (x)      |   | [ |     |   |  |  |  |  |

|----------|---|----------|---|---|-----|---|--|--|--|--|

|          | • | ••       |   | - |     | a |  |  |  |  |

| }        |   | _        | r |   |     | W |  |  |  |  |

| l e l    |   | e {<br>= | • | + | b;  |   |  |  |  |  |

| }        |   |          | - |   | - , |   |  |  |  |  |

| У        | = | а        | + | b | ;   |   |  |  |  |  |

|          |   |          |   |   |     |   |  |  |  |  |

at a higher-level, ve cannot replace: y = a + b. with y = x;

| x = a + b;<br>if (x) { |       |

|------------------------|-------|

|                        | But   |

| }                      | not r |

| else {                 |       |

|                        | can b |

| }                      |       |

| y = a + b;             |       |

|                        |       |

```

But if a and b are

not redefined, then

y = a + b;

can be replaced with

y = x;

```

### Next Class

- A basic-block local optimization

- local value numbering

- Friday: Control flow graphs and intra-block analysis