# CSE113: Parallel Programming

March 1, 2023

#### • Topics:

- Intro to module 4

- Barriers

#### Announcements

- Midterm grades are out

- Let us know within 1 week if there are issues

- We are working on HW 2 grades and will strive to get them released by Monday

- Homework 3 is due today (last late day)

- We are hoping to get HW 4 assigned today

- There are some issues with the server we are trying to work out

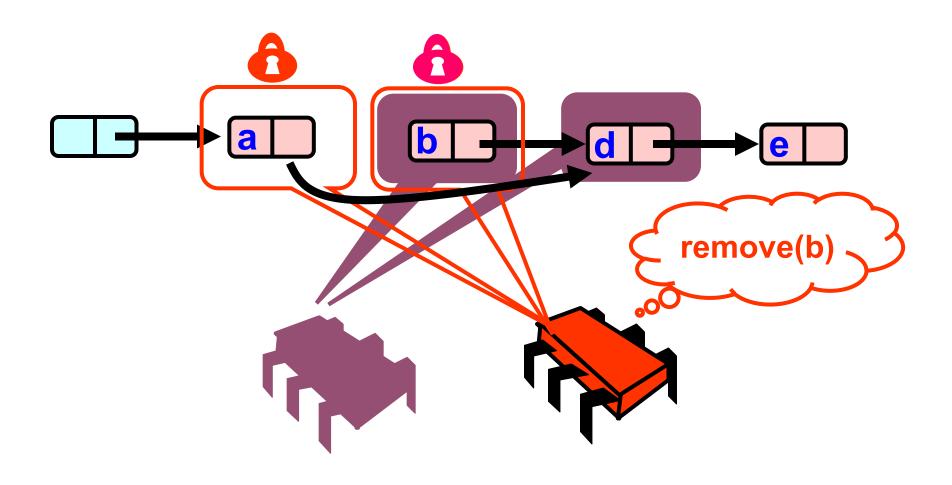

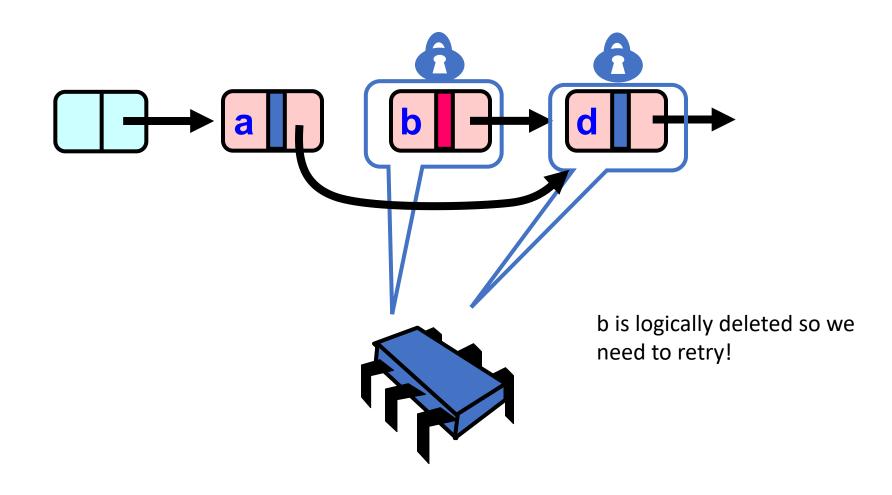

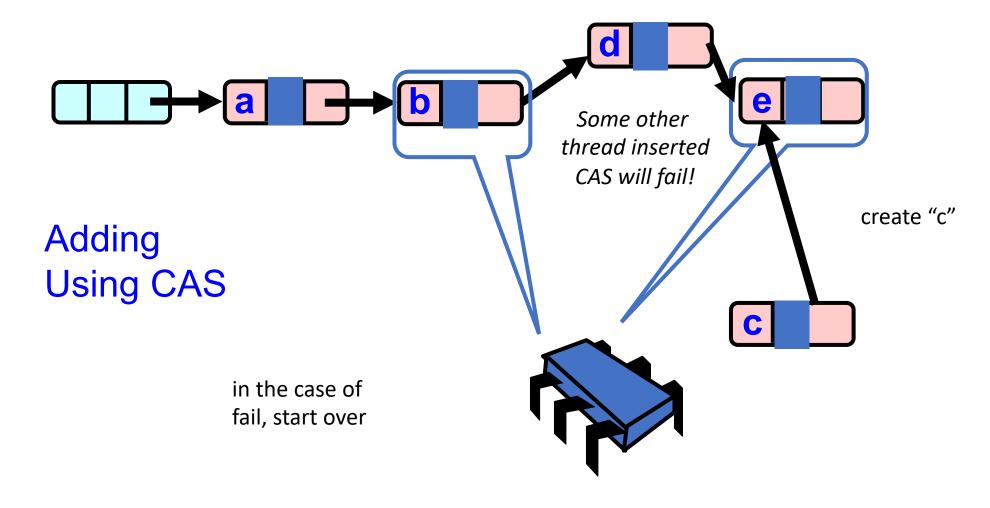

When a CAS operation fails in a lock-free linked list, the implementation should:

- on the same CAS (like a mutex), it will eventually succeed

- throw an exception

- oretry the operation from the start, even if it means traversing the list again

- The CAS operation will never fail because it is an atomic operation

| An object wrapped in the C++ atomic template allows you to: |

|-------------------------------------------------------------|

| Check all that apply                                        |

|                                                             |

| atomically execute method calls                             |

| ☐ load and store the object atomically                      |

| perform atomic CAS on the object                            |

| □ locks each method call automatically                      |

| Which are possible ways that hardware implements RMW operations? check all that apply: |

|----------------------------------------------------------------------------------------|

| special loads and stores that track if there has been a conflict                       |

| sleeping all other threads while one thread accesses the location                      |

| ☐ having the hardware lock the cache line                                              |

| ☐ flushing the pipeline to avoid ILP interleavings                                     |

It is the end of module 3: concurrent data structures:

Feel free to write a few sentences about how you found the module, e.g. what you found most interesting, what you found unclear, etc.

See you on Wednesday to start module 4!

#### Review

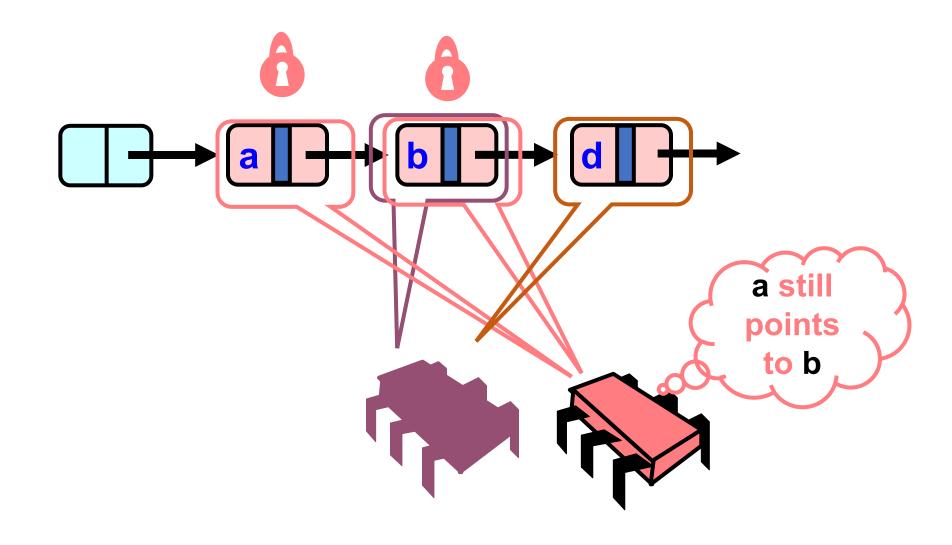

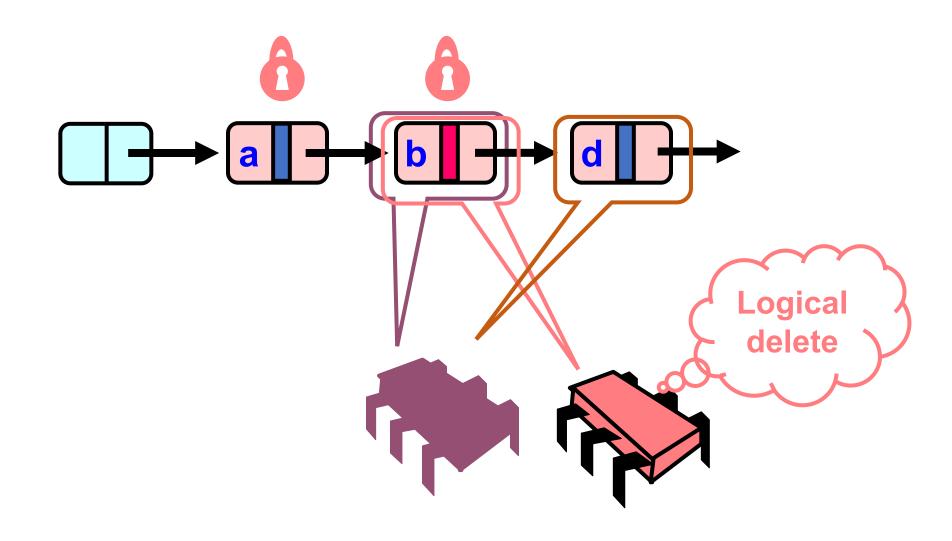

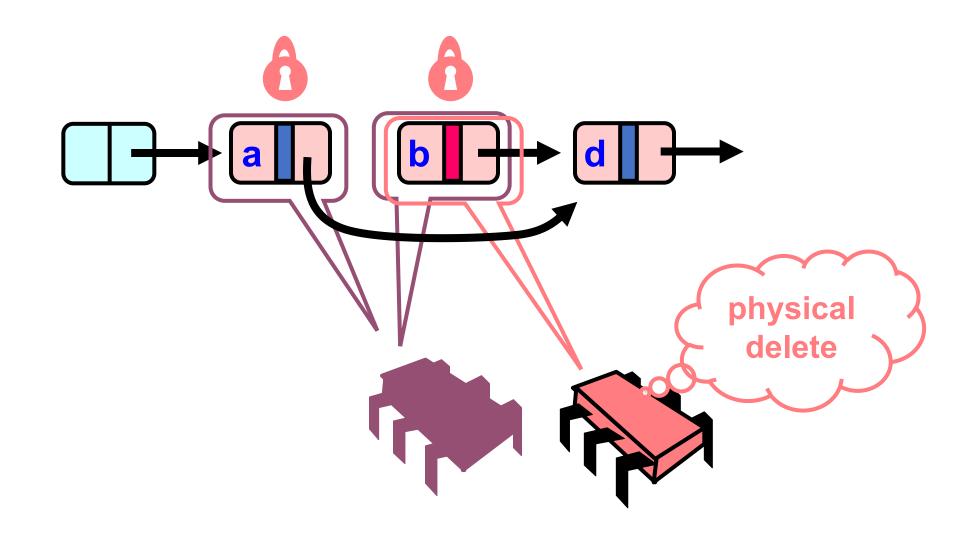

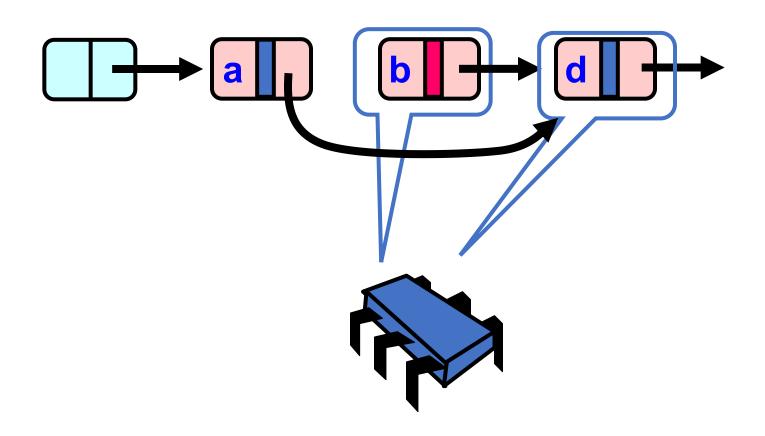

Optimizing the concurrent set

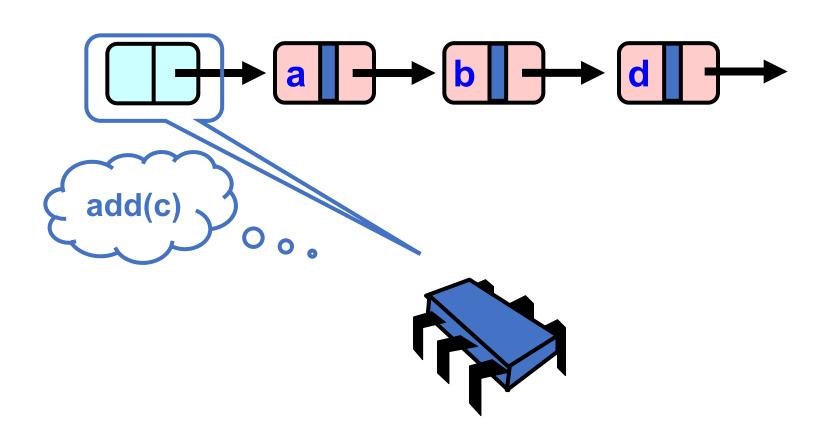

# Single traversal operations

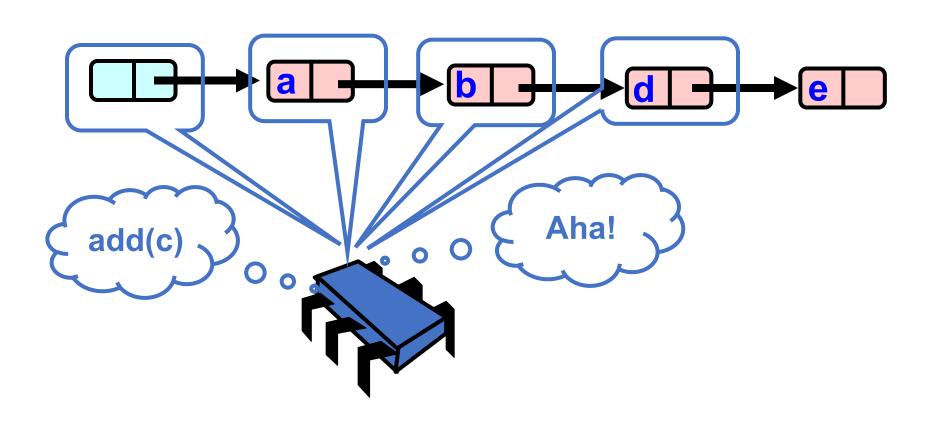

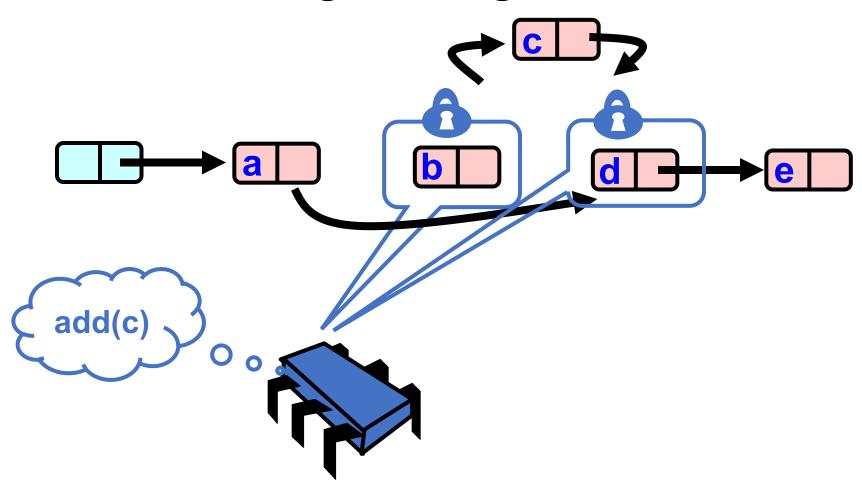

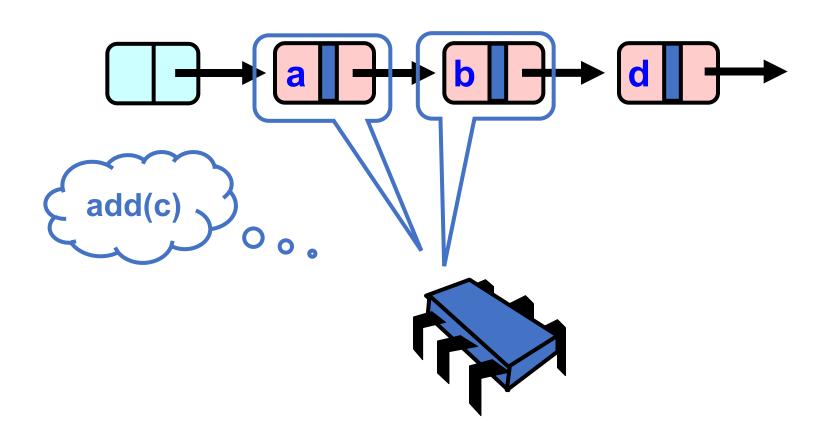

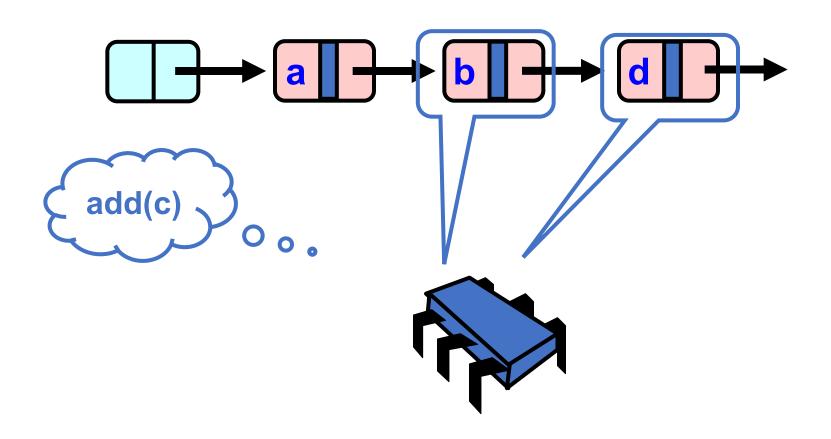

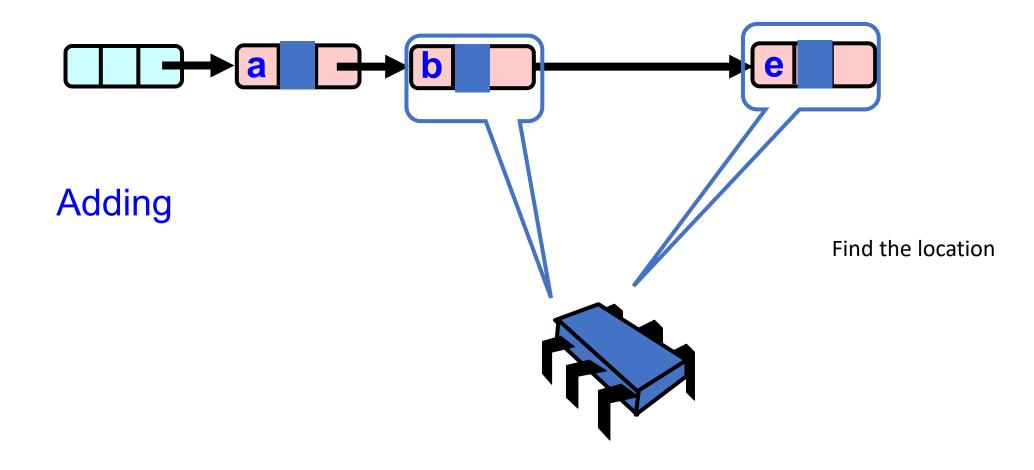

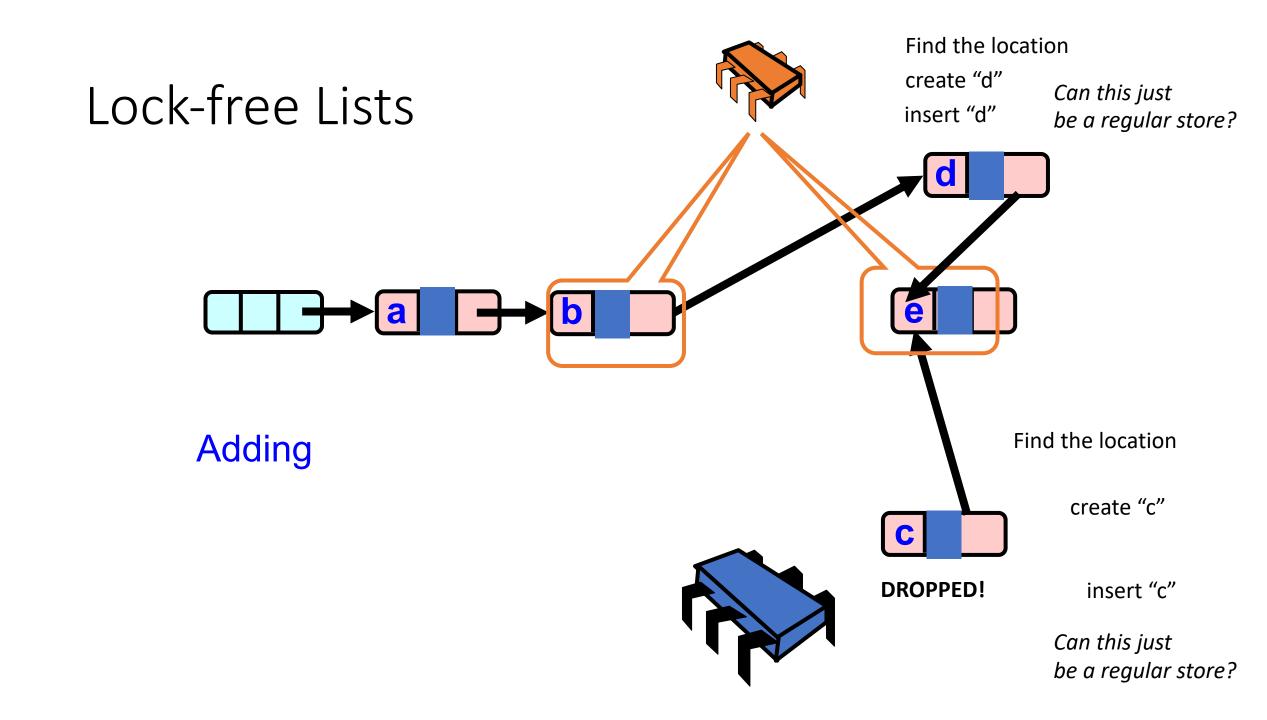

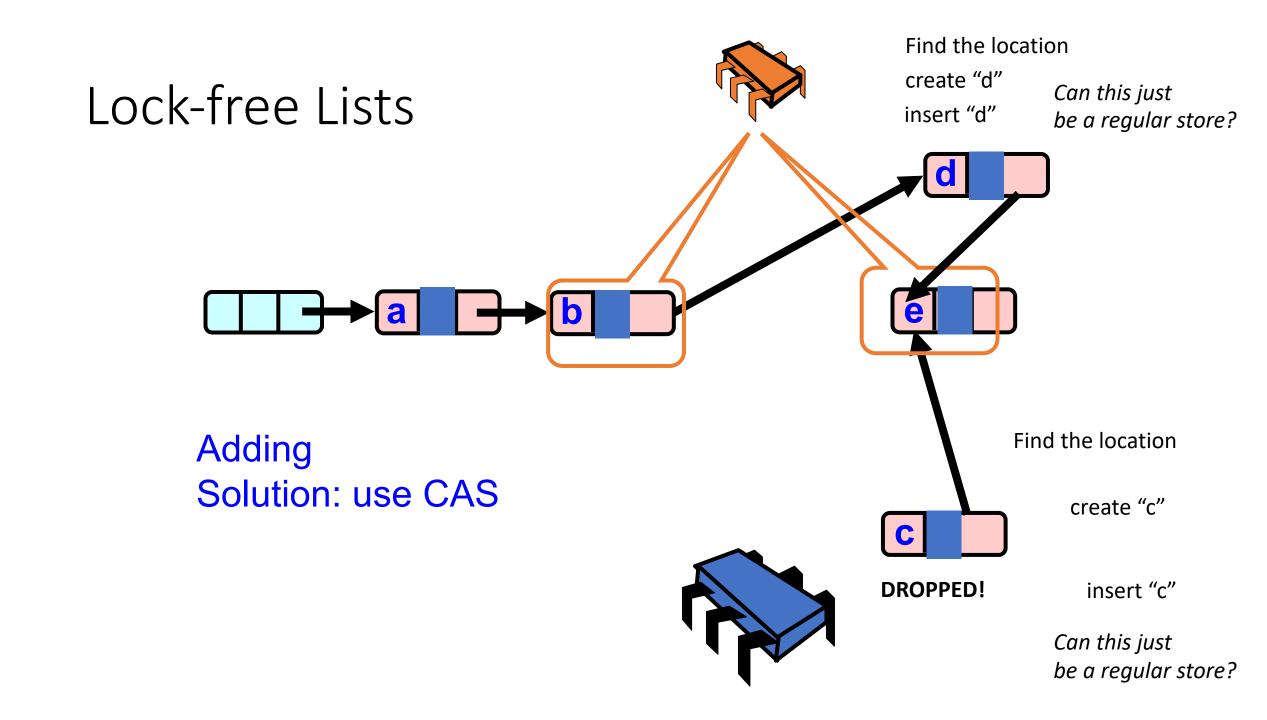

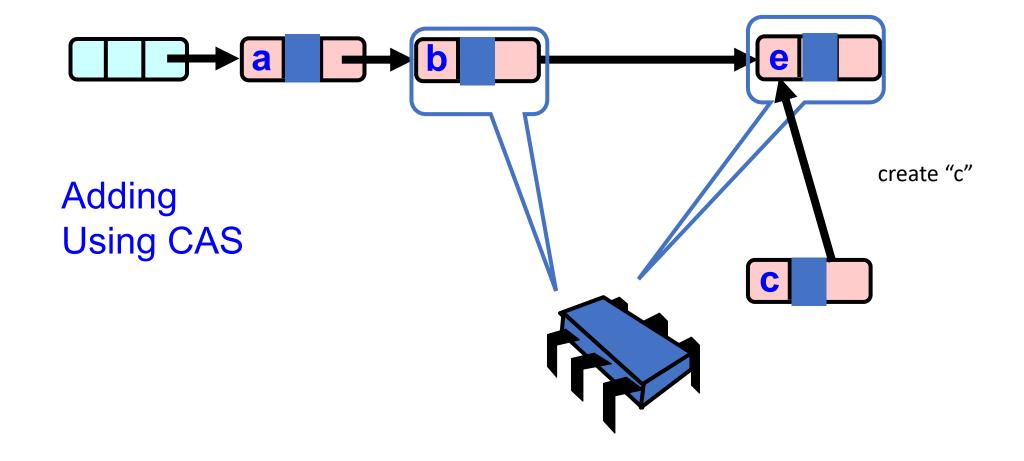

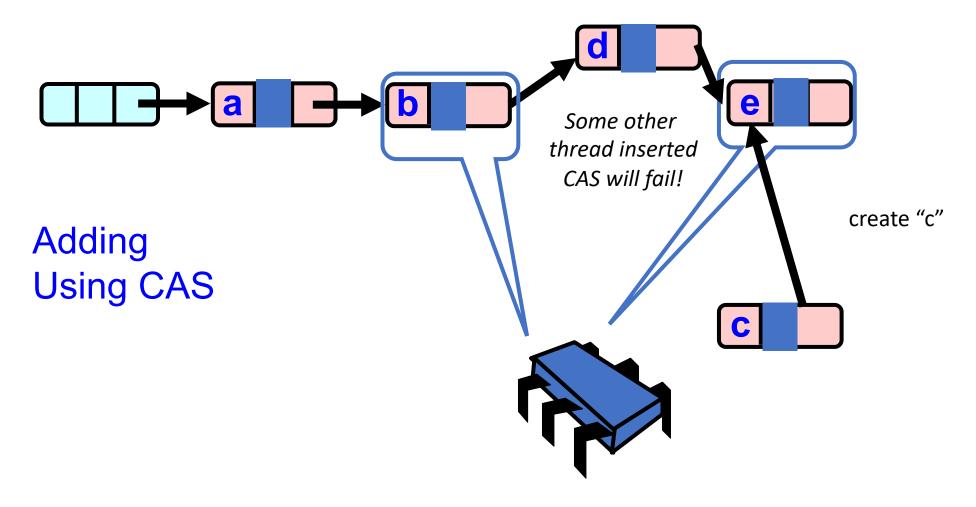

#### CAS based insertion

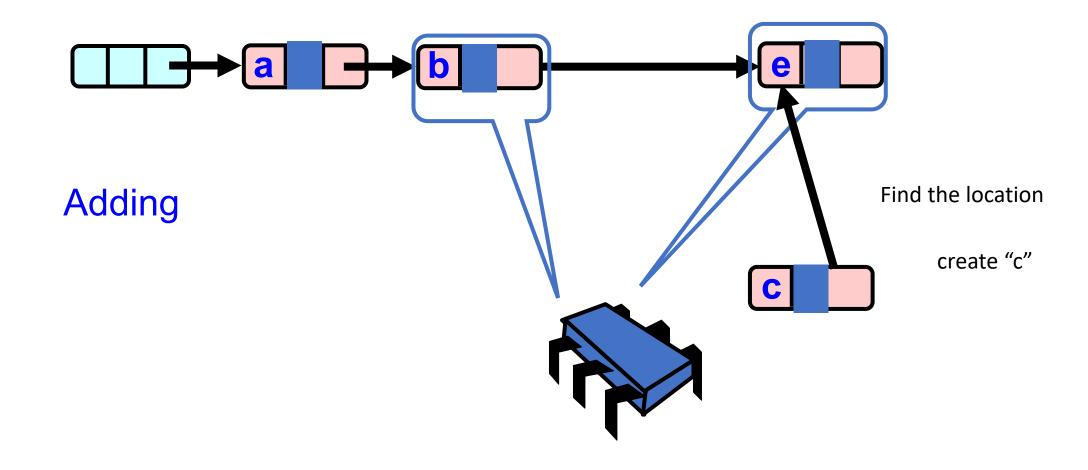

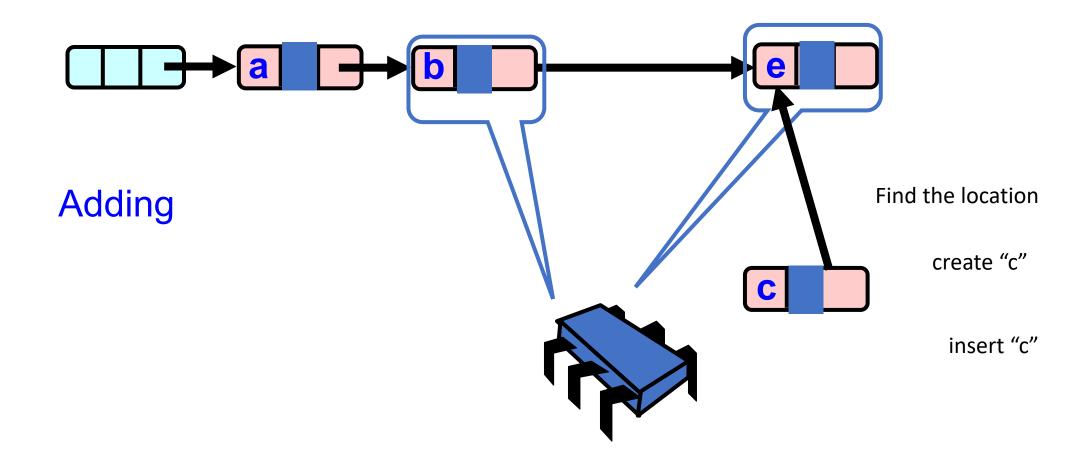

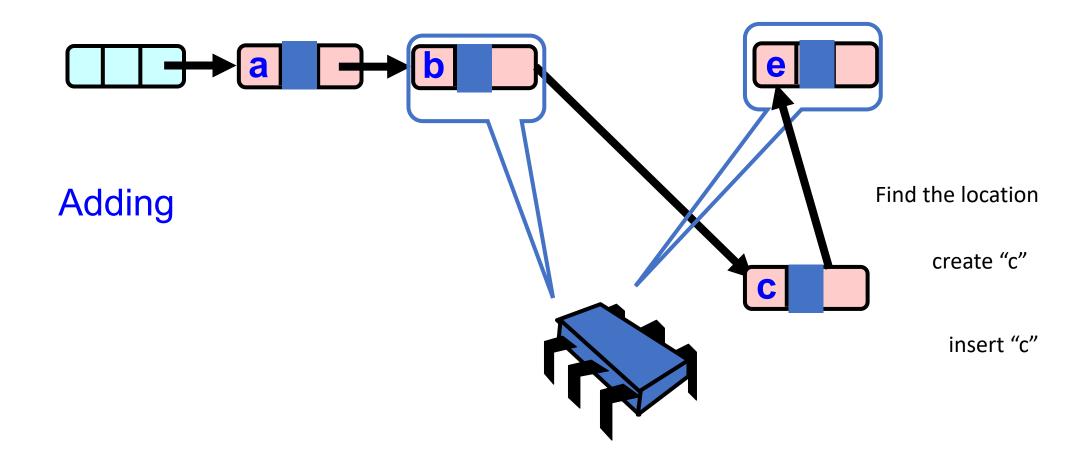

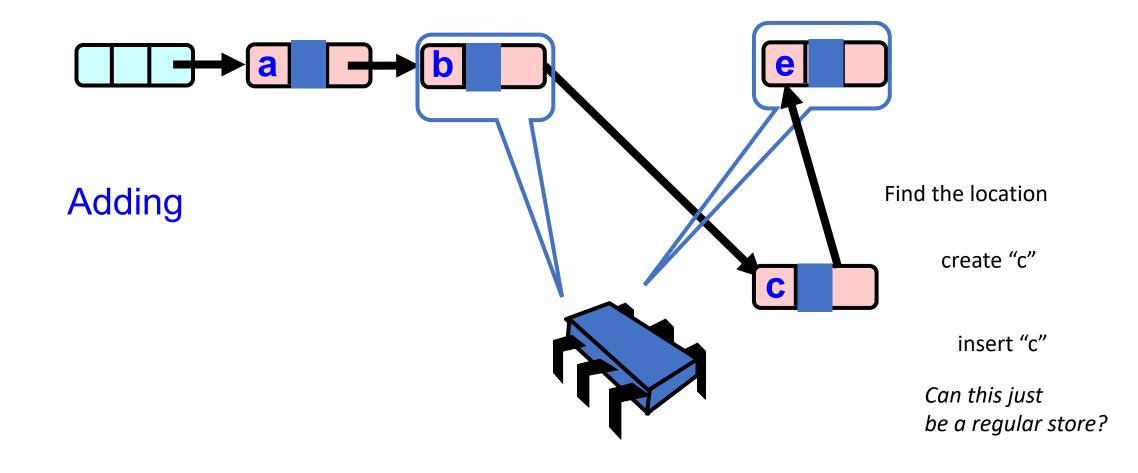

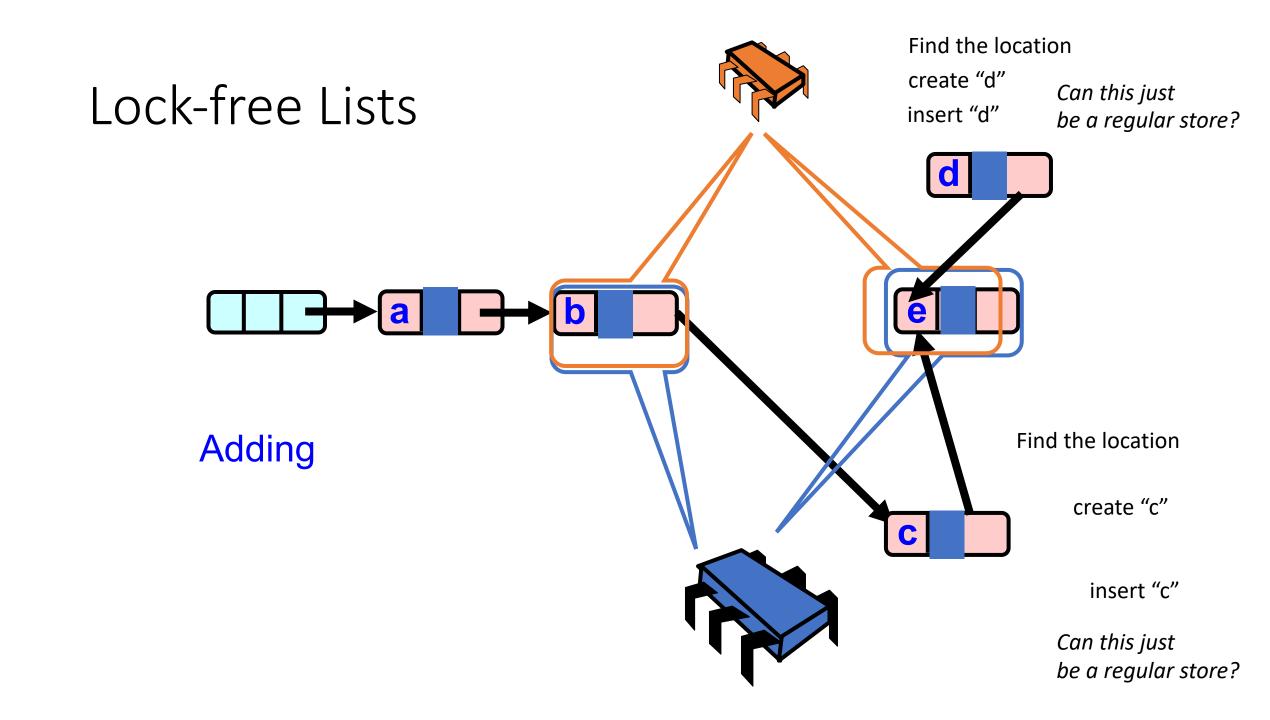

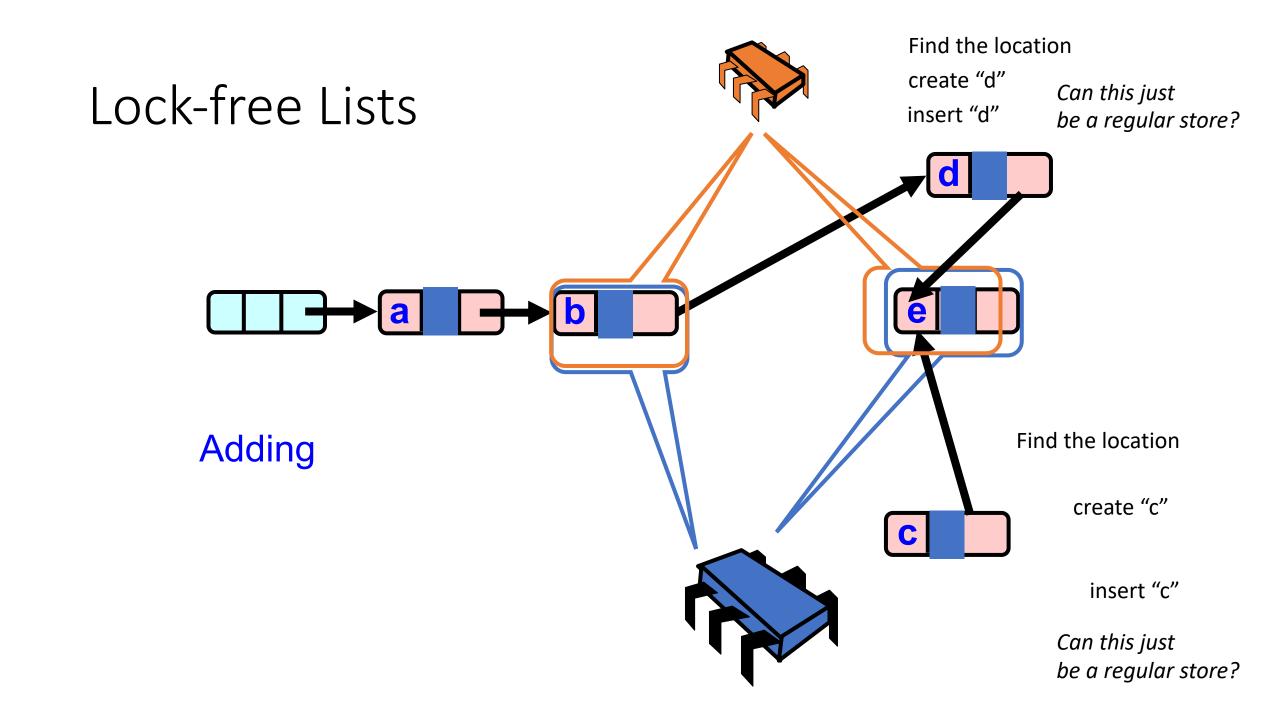

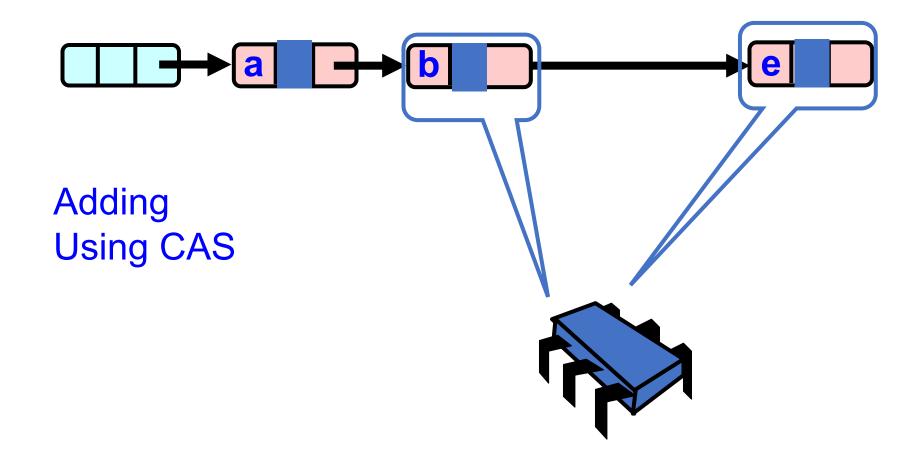

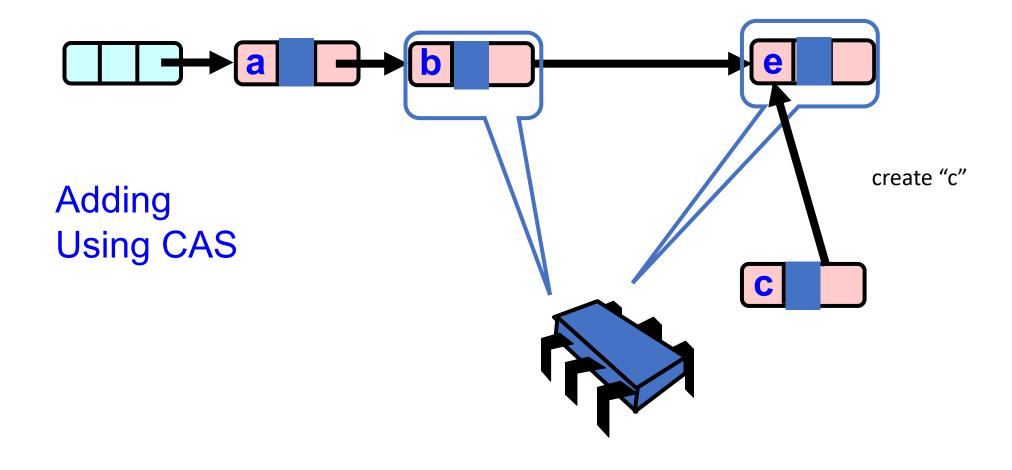

**Adding**

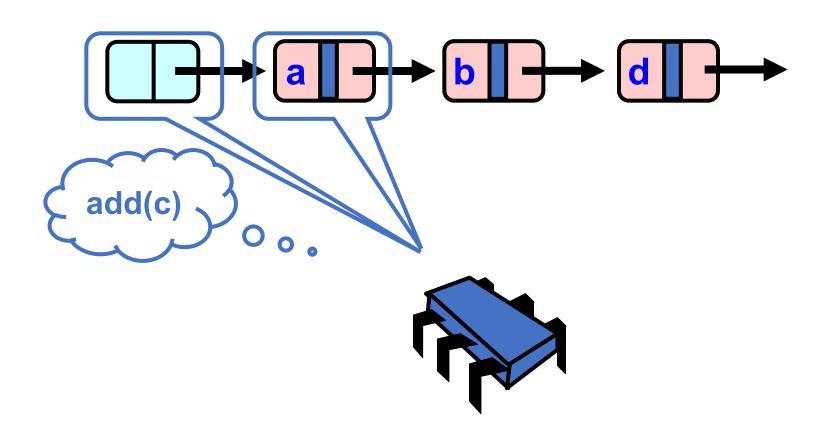

Find the location

Cache your insertion

point!

b.next == e

Find the location

Cache your insertion

point!

b.next == e

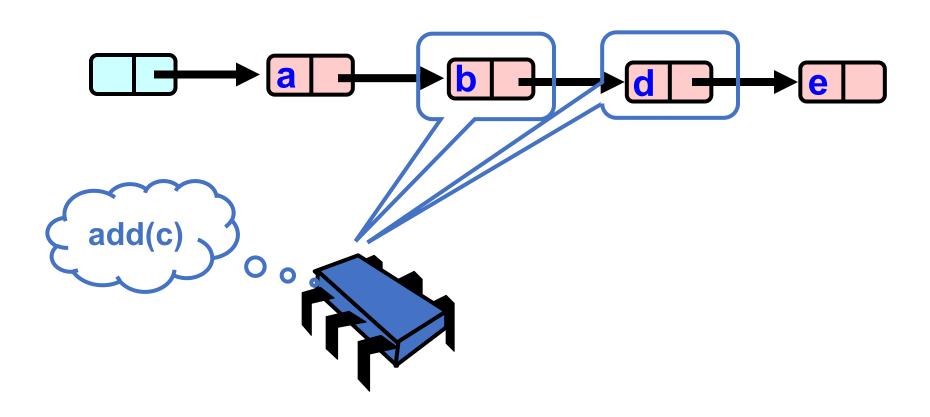

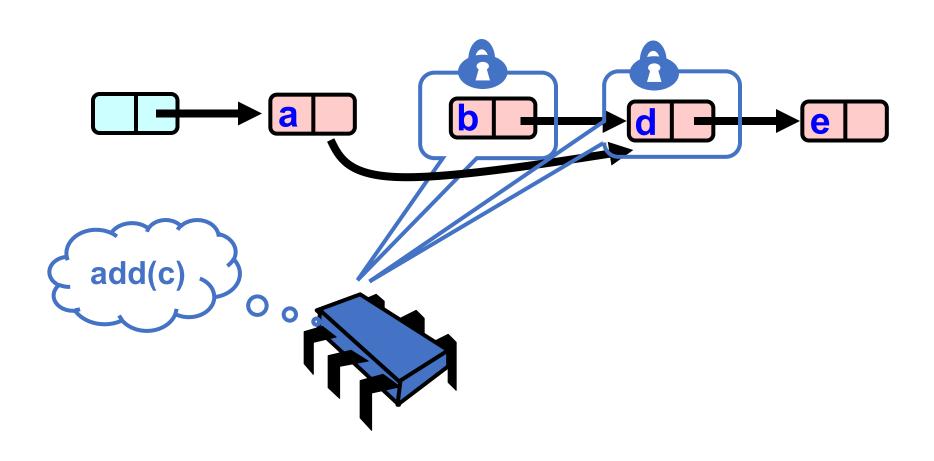

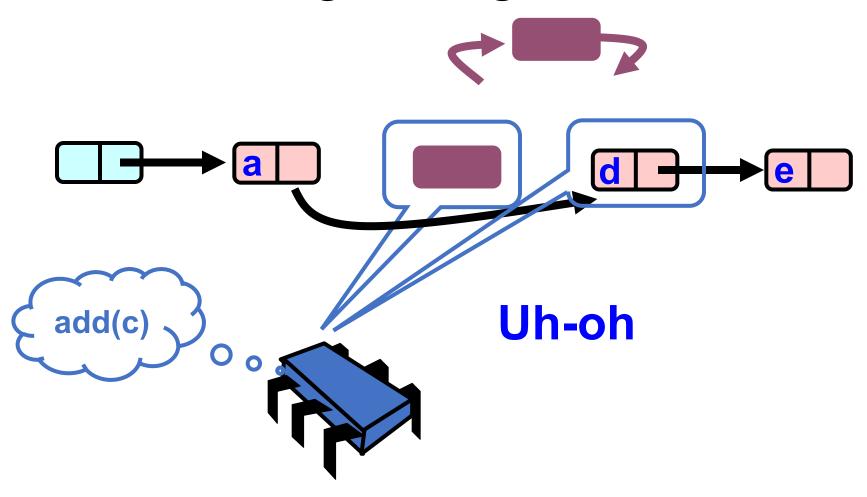

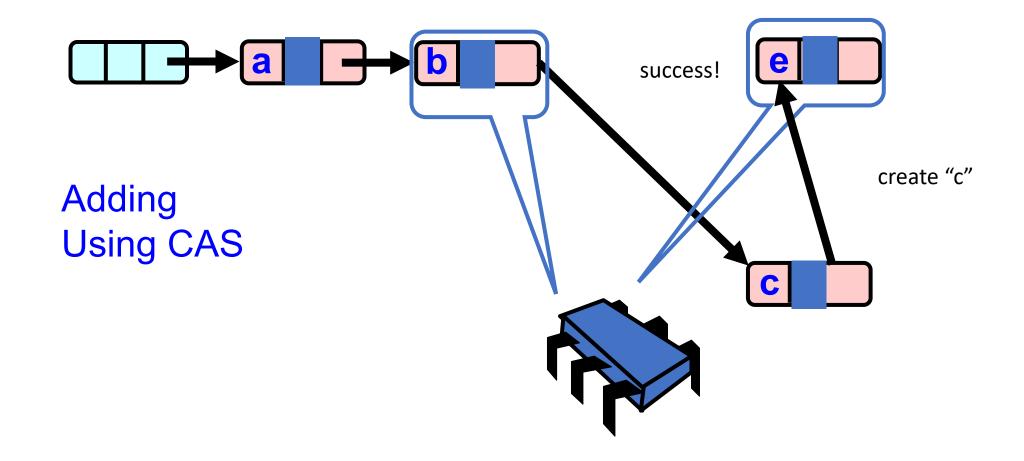

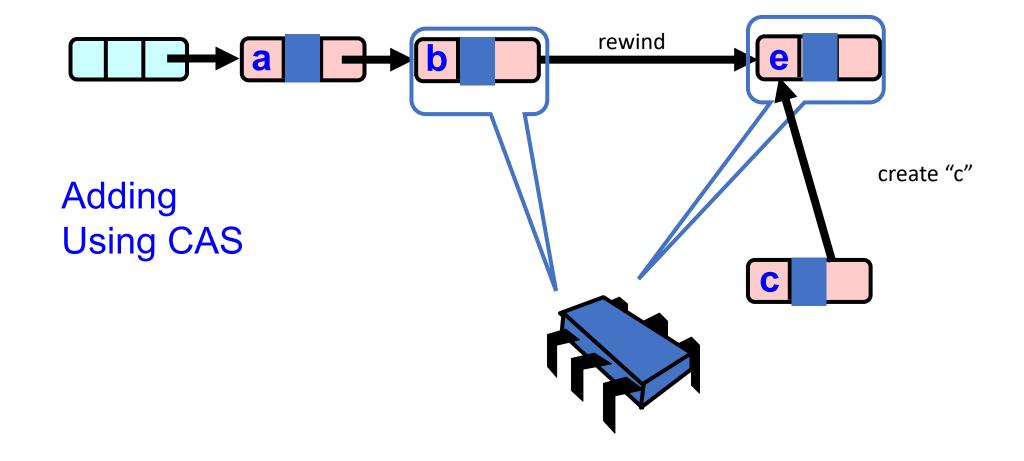

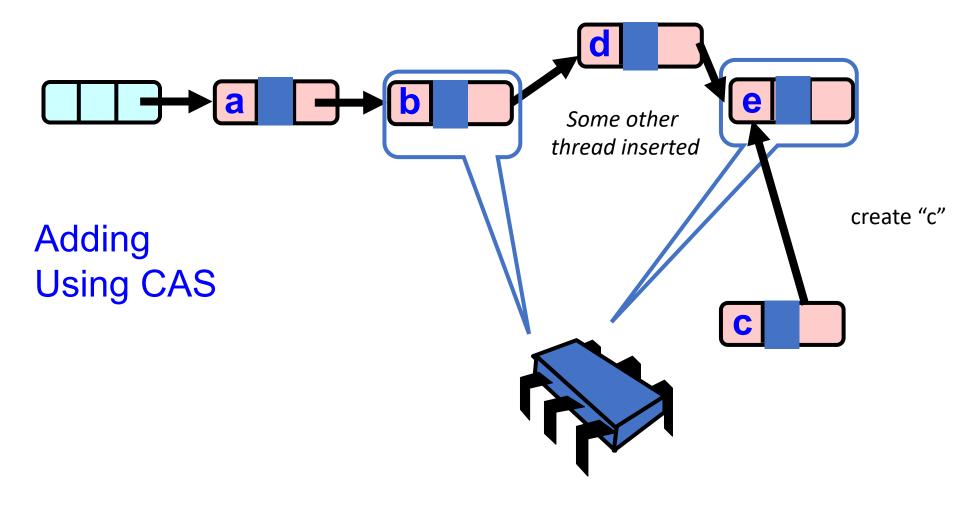

Only insert if your insertion point is valid!

CAS(b.next, e, c);

Find the location Cache your insertion point!

b.next == e

Only insert if your insertion point is valid!

CAS(b.next, e, c);

Find the location Cache your insertion point!

b.next == e

Only insert if your insertion point is valid!

CAS(b.next, e, c);

Find the location Cache your insertion point!

b.next == e

Only insert if your insertion point is valid!

CAS(b.next, e, c);

Find the location Cache your insertion point!

b.next == e

Only insert if your insertion point is valid!

CAS(b.next, e, c);

Find the location Cache your insertion point!

b.next == e

Only insert if your insertion point is valid!

CAS(b.next, e, c);

Find the location Cache your insertion point!

b.next == e

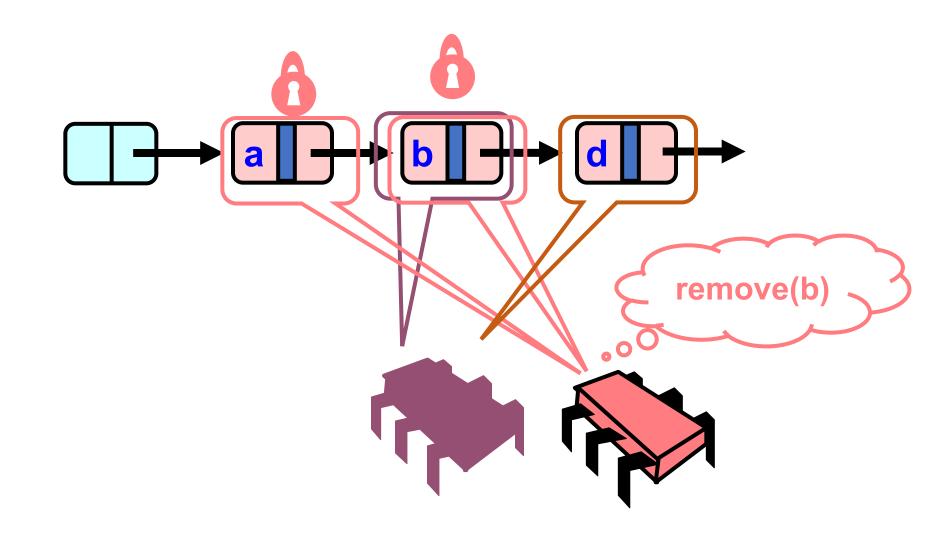

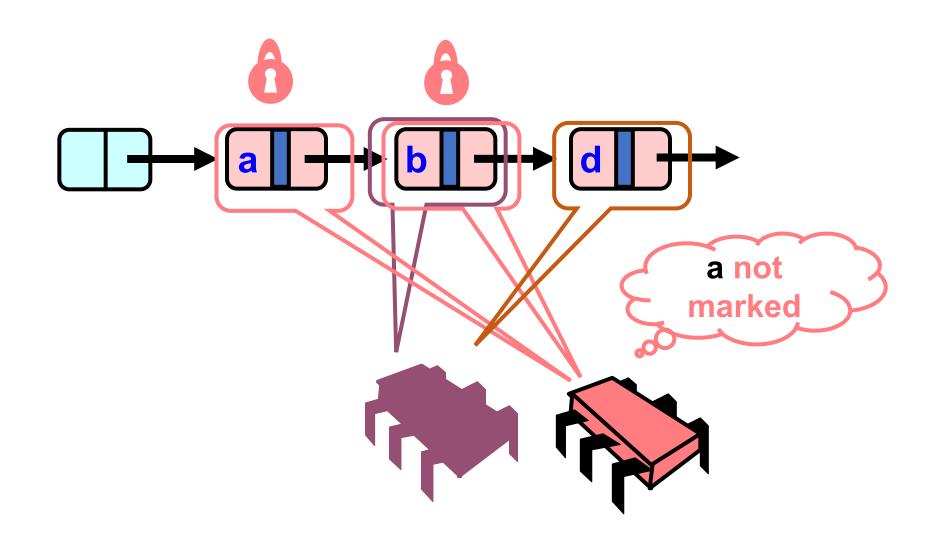

#### Further considerations

need to include "valid bit" in compare and swap to make sure the node is still valid

Can "pack the bit" into the address (there will always be room because addresses are byte addressable, and addresses 8 bytes)

More details in the book!

### Schedule

• Module 4 introduction

- Barriers

- Specification

- Implementation

### Schedule

Module 4 introduction

- Barriers

- Specification

- Implementation

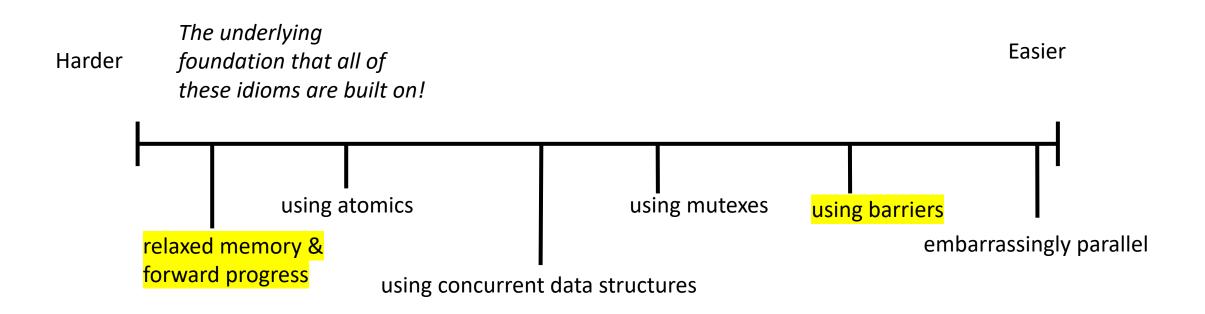

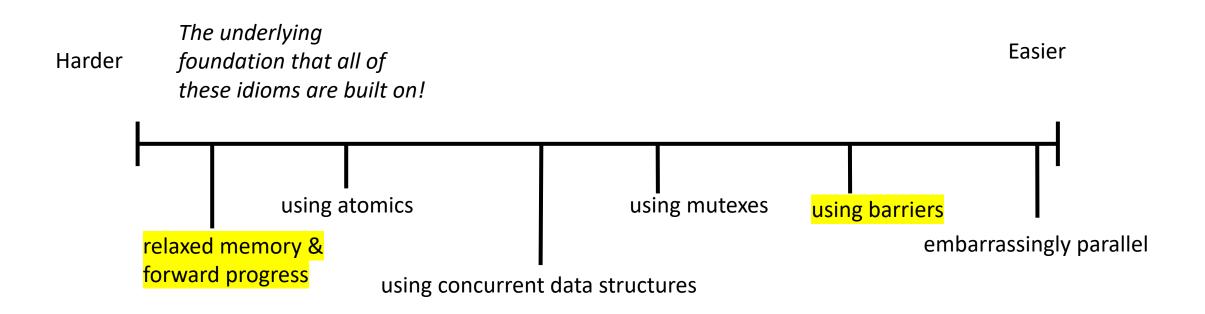

#### Mental model of concurrency

- Functional

- Interleavings events from different threads can interleave

- Atomicity what events are indivisible?

- Specifications how can we create useful abstractions (mutexes, concurrent data structures)

- Performance

- Increase parallelism judicious use of mutexes, load balancing

- Cache behaviors threads should try to utilize their own cache lines

- Operating system yielding/sleeping threads

- Architectural details instruction-level parallelism

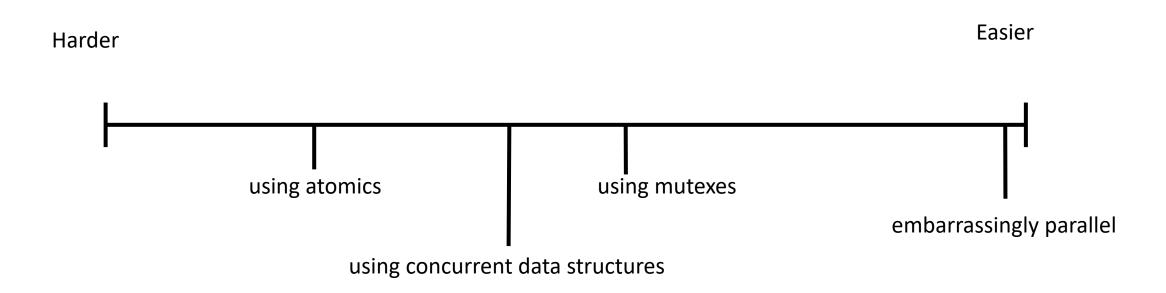

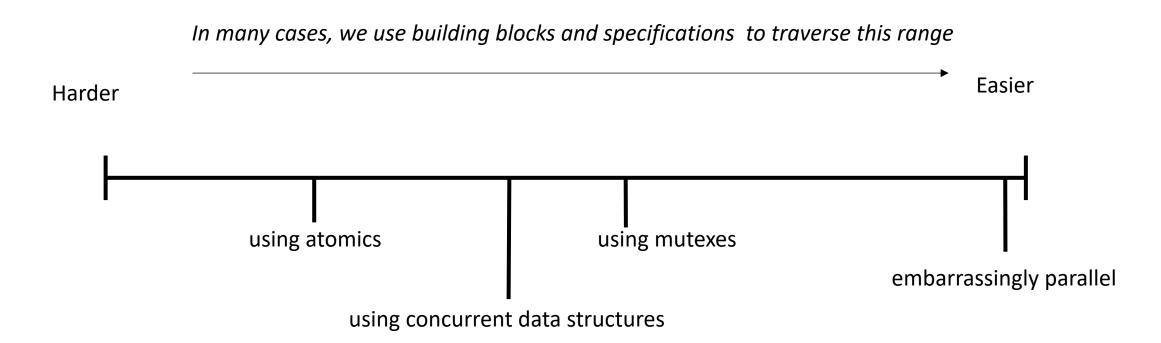

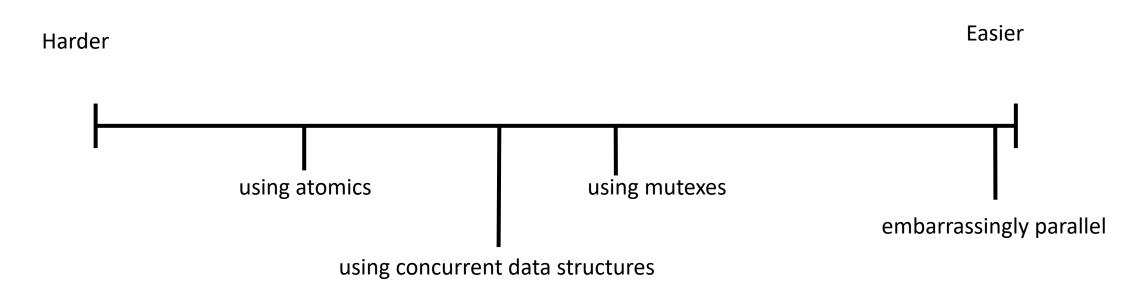

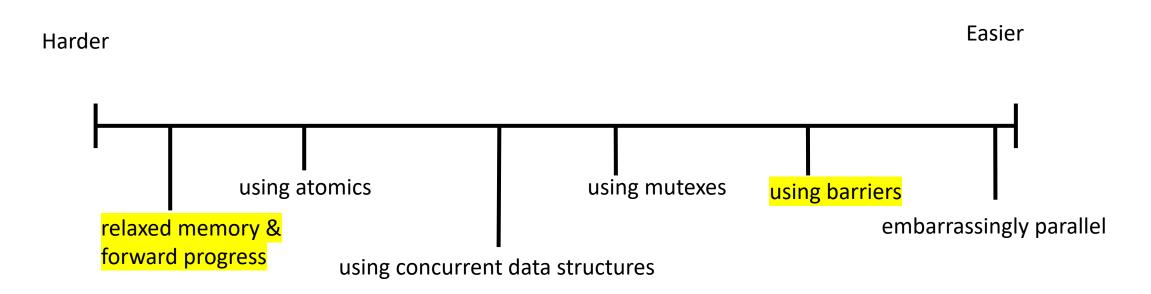

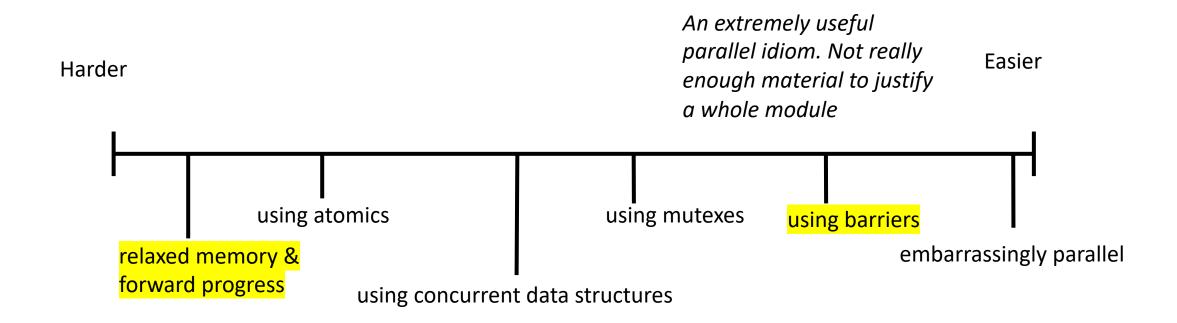

Depending on your needs, programs become more/less complex to reason about.

• Depending on your needs, programs become more/less complex to reason about.

Depending on your needs, programs become more/less complex to reason about.

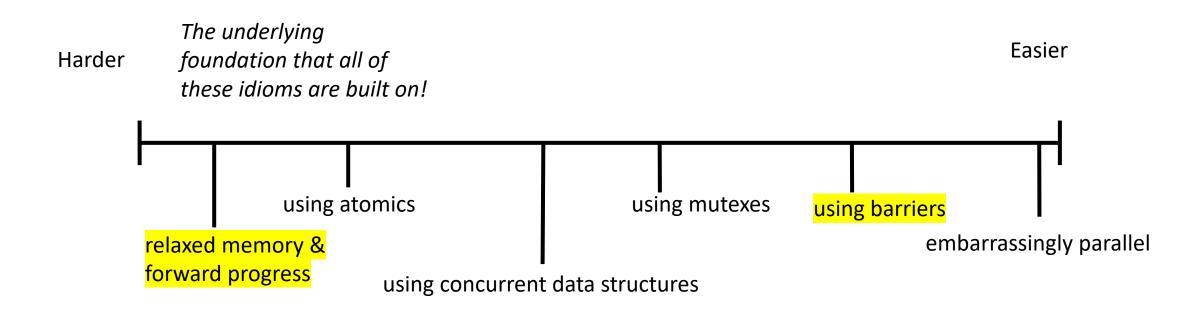

To get a more complete picture, we will fill in some of the gaps here

Depending on your needs, programs become more/less complex to reason about.

To get a more complete picture, we will fill in some of the gaps here

Depending on your needs, programs become more/less complex to reason about.

Depending on your needs, programs become more/less complex to reason about.

On newer architectures, you may only get specifications about the relaxed memory and progress. It is up to the user to implement their own atomics, mutexes, concurrent data structures, etc!

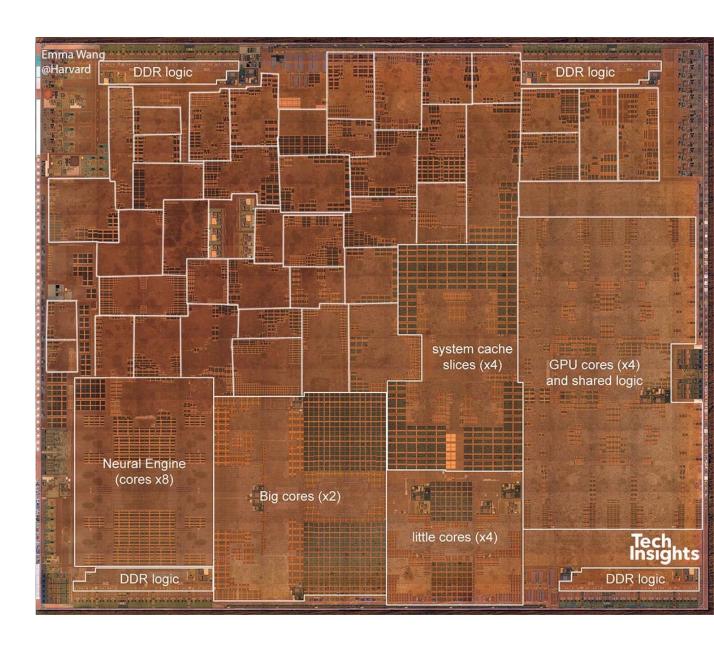

### Modern chips

• From David Brooks lab at Harvard:

http://vlsiarch.eecs.harvard. edu/research/accelerators/di e-photo-analysis/

GPUs/accelerators will have different guarantees w.r.t. atomics and memory orderings

#### Historical issues on Nvidia GPUs

Issue implementing a concurrent data structure related to memory orderings

Issue implementing a mutex relating to memory orderings

#### Historical issues on Nvidia GPUs

In both cases, they had reasoned about their implementations exactly how we have! The issues came from lower in the stack: memory orderings

### running a mutex on an iPad GPU?

This one has to do with functional properties of the scheduler

video demo

On newer architectures, you may only get specifications about the relaxed memory and progress. It is up to the user to implement their own atomics, mutexes, concurrent data structures, etc!

### Schedule

• Module 4 introduction

- Barriers

- Specification

- Implementation

- Why do barriers fit into this module: "Reasoning About Parallel Computing"?

- Relaxed Memory Models make reasoning about parallel computing HARD

- Barriers make it EASIER (at the cost of performance potentially)

- A barrier is a concurrent object (like a mutex):

- Only one method: barrier (called await in the book)

- Separates computational phases

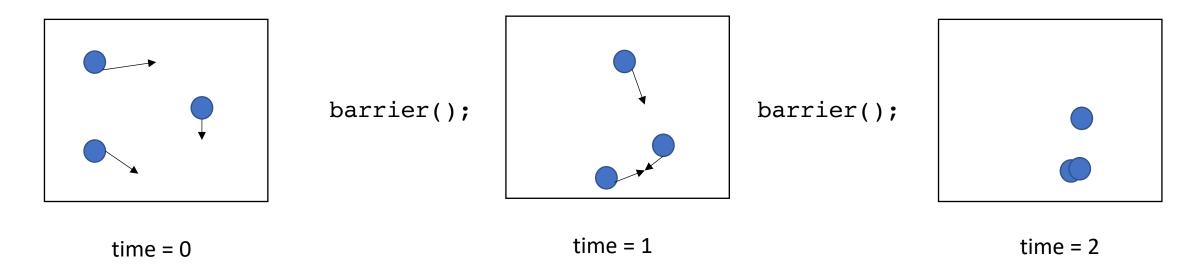

My current favorite: particle simulation

by Yanwen Xu

My current favorite: particle simulation

time = 1

time = 2

My current favorite: particle simulation

time = 0

time = 1

time = 2

at each time, compute new positions for each particle (in parallel)

My current favorite: particle simulation

at each time, compute new positions for each particle (in parallel)

But you need to wait for all particles to be computed before starting the next time step

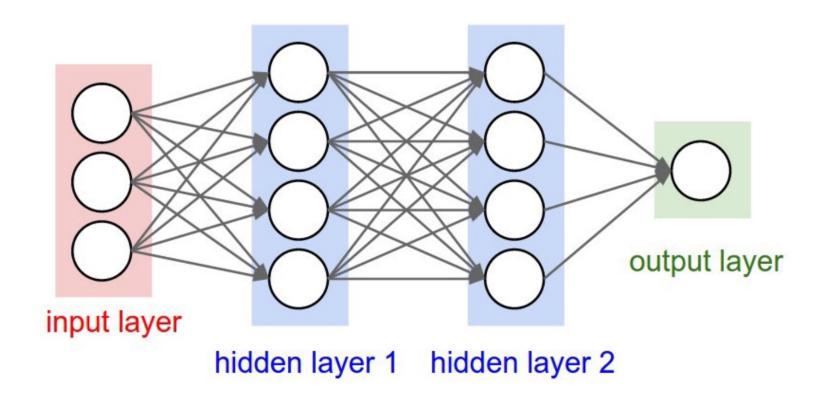

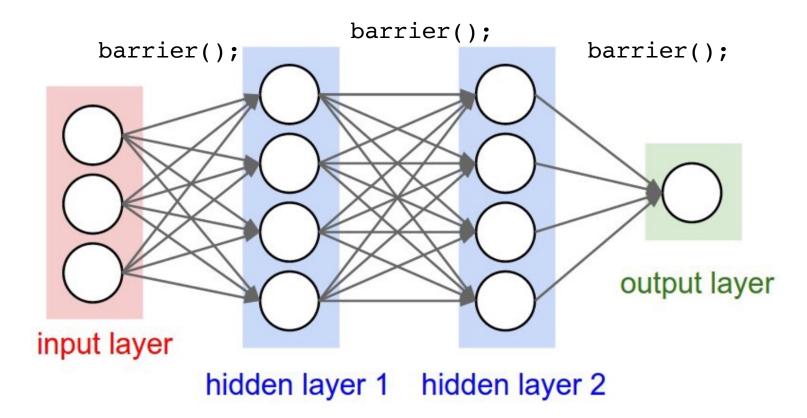

Deep neural networks

Deep neural networks

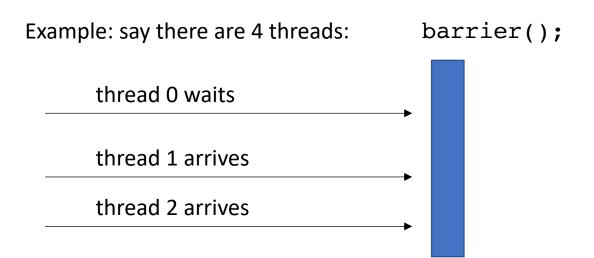

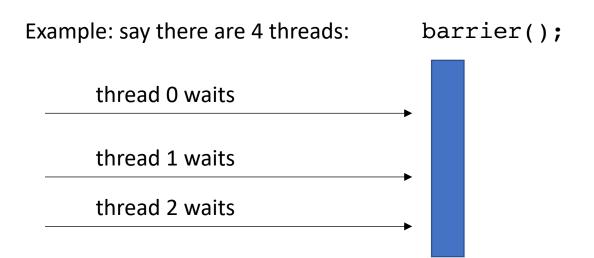

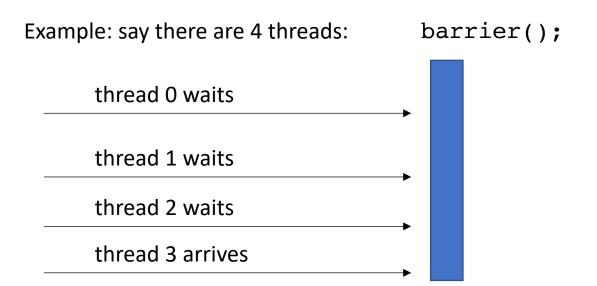

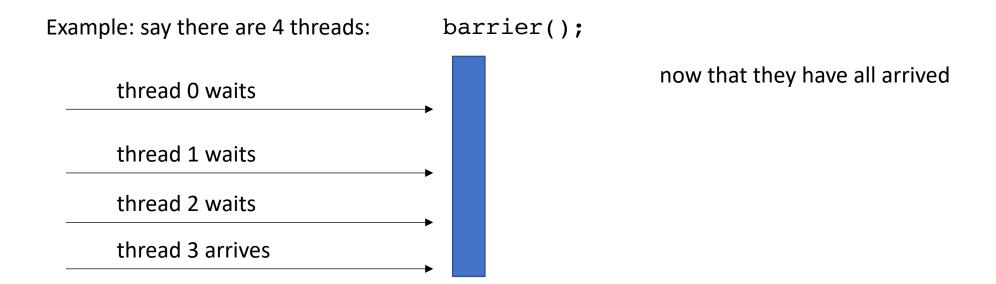

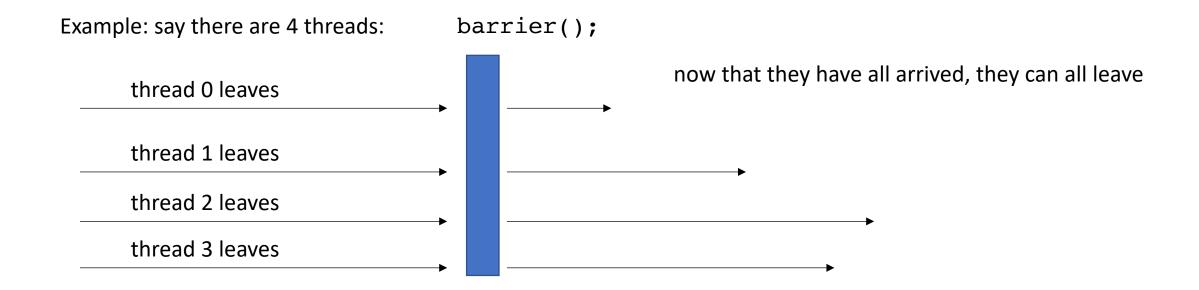

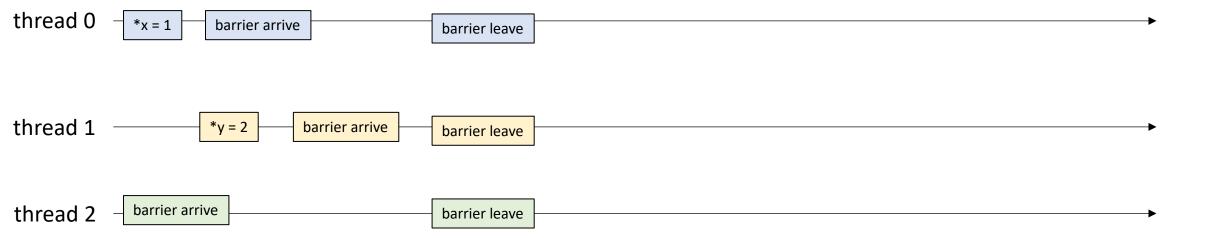

- Intuition: threads stop and wait for each other:

- Threads *arrive* at the barrier

- Threads wait at the barrier

- Threads *leave* the barrier once all other threads have arrived

- Intuition: threads stop and wait for each other:

- Threads *arrive* at the barrier

- Threads wait at the barrier

- Threads leave the barrier once all other threads have arrived

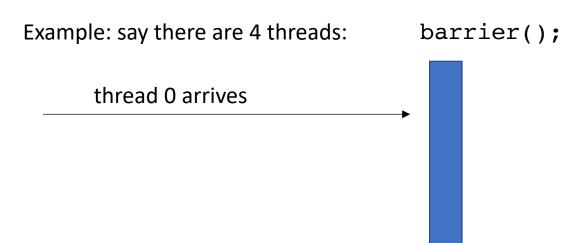

Example: say there are 4 threads: barrier();

- Intuition: threads stop and wait for each other:

- Threads *arrive* at the barrier

- Threads wait at the barrier

- Threads leave the barrier once all other threads have arrived

- Intuition: threads stop and wait for each other:

- Threads *arrive* at the barrier

- Threads wait at the barrier

- Threads leave the barrier once all other threads have arrived

- Intuition: threads stop and wait for each other:

- Threads *arrive* at the barrier

- Threads wait at the barrier

- Threads leave the barrier once all other threads have arrived

- Intuition: threads stop and wait for each other:

- Threads *arrive* at the barrier

- Threads wait at the barrier

- Threads leave the barrier once all other threads have arrived

- Intuition: threads stop and wait for each other:

- Threads *arrive* at the barrier

- Threads wait at the barrier

- Threads leave the barrier once all other threads have arrived

- Intuition: threads stop and wait for each other:

- Threads *arrive* at the barrier

- Threads wait at the barrier

- Threads leave the barrier once all other threads have arrived

```

A more formal specification

```

Given a global barrier B and a global memory location x where initially \*x = 0;

First, what would we expect var to be after this program?

```

Thread 1:

B.barrier();

var = *x;

```

```

thread 0

```

Thread 0:

\*x = 1;

B.barrier();

thread 1 ----

```

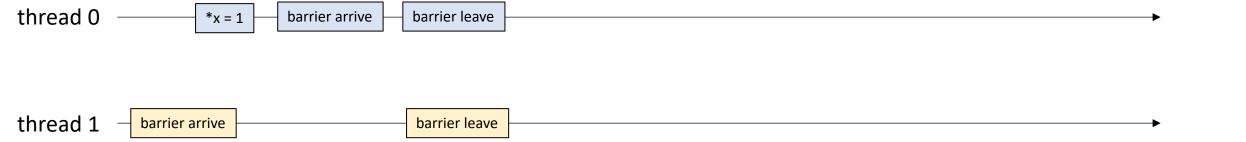

A more formal specification

```

Given a global barrier B and a global memory location x where initially \*x = 0;

```

Thread 1:

B.barrier();

var = *x*

```

gives an event: barrier arrive

```

thread 0 ----

```

```

thread 1 barrier arrive

```

Thread 0:

\*x = 1; B.barrier();

#### A more formal specification

Given a global barrier B and a global memory location x where initially \*x = 0;

```

<u>Thread 0:</u>

*x = 1;

B.barrier();

```

```

Thread 1:

B.barrier();

var = *x;

```

gives an event: barrier arrive

barrier arrive needs to wait for all threads to arrive (similar to how a mutex request must wait for another to release)

```

thread 0

```

```

thread 1 — barrier arrive

```

```

A more formal specification

```

Given a global barrier B and a global memory location x where initially \*x = 0;

```

thread 0 *x = 1

```

```

thread 1 barrier arrive

```

```

A more formal specification

```

Given a global barrier B and a global memory location x where initially \*x = 0;

```

Thread 0:

*x = 1;

B.barrier();

```

```

thread 0 *x = 1 barrier arrive

```

thread 1 barrier arrive

```

<u>Thread 0:</u>

*x = 1;

B.barrier();

```

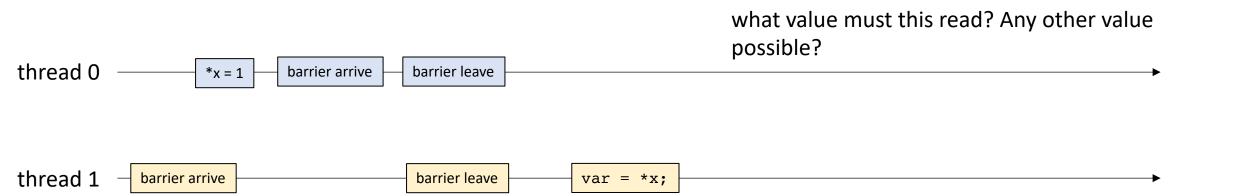

A more formal specification

Given a global barrier B and a global memory location x where initially \*x = 0;

```

Thread 1:

B.barrier();

var = *x;

```

now that all threads have arrived: They can leave (1 event at the same time)

#### A more formal specification

Thread 0:

\*x = 1;

B.barrier();

Given a global barrier B and a global memory location x where initially \*x = 0;

```

Thread 1:

B.barrier();

var = *x;

```

This finishes the barrier execution

```

thread 0 *x = 1 barrier arrive barrier leave barrier leave barrier leave

```

```

A more formal specification

```

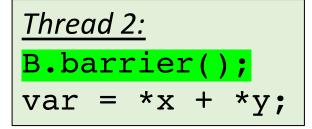

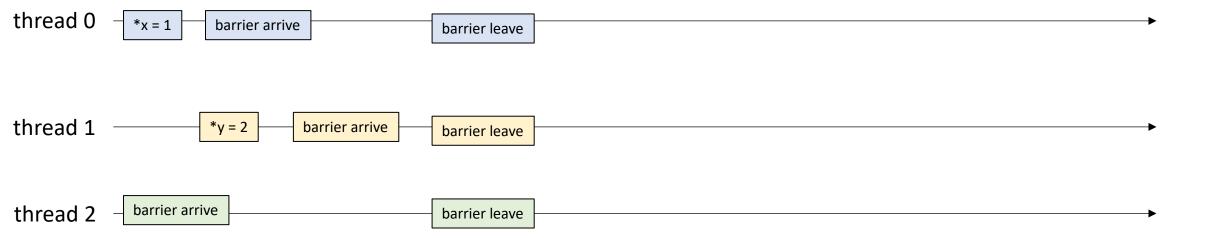

Given a global barrier B and a global memory location x where initially \*x = 0;

```

Thread 0:

*x = 1;

B.barrier();

```

```

<u>Thread 1:</u>

*y = 2;

B.barrier();

```

```

<u>Thread 2:</u>

B.barrier();

var = *x + *y;

```

```

thread 0

thread 1

```

```

Thread 0:

*x = 1;

B.barrier();

```

barrier arrive

```

<u>Thread 1:</u>

*y = 2;

B.barrier();

```

```

<u>Thread 2:</u>

B.barrier();

var = *x + *y;

```

```

thread 0

thread 1

```

```

<u>Thread 0:</u>

*x = 1;

B.barrier();

```

barrier arrive

```

Thread 1:

*y = 2;

B.barrier();

```

```

<u>Thread 2:</u>

B.barrier();

var = *x + *y;

```

```

thread 0 *x=1 thread 1 *y=2

```

```

<u>Thread 0:</u>

*x = 1;

B.barrier();

```

```

Thread 1:

*y = 2;

B.barrier();

```

```

<u>Thread 2:</u>

B.barrier();

var = *x + *y;

```

```

<u>Thread 0:</u>

*x = 1;

B.barrier();

```

```

Thread 1:

*y = 2;

B.barrier();

```

They've all arrived

```

<u>Thread 0:</u>

*x = 1;

B.barrier();

```

```

Thread 1:

*y = 2;

B.barrier();

```

```

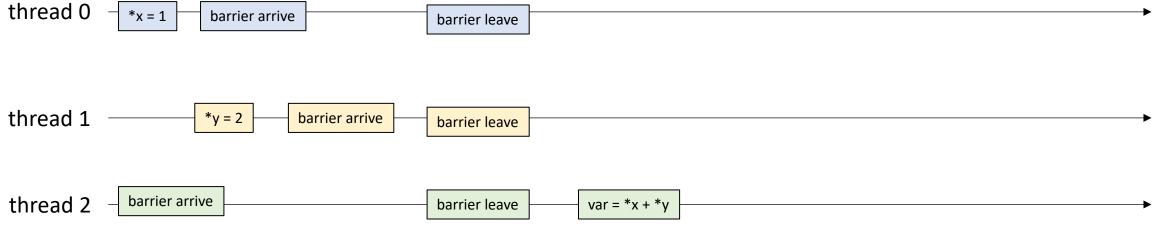

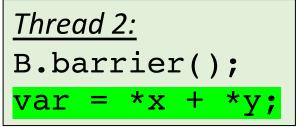

Thread 2:

B.barrier();

var = *x + *y;

```

They've all arrived

```

<u>Thread 0:</u>

*x = 1;

B.barrier();

```

```

<u>Thread 1:</u>

*y = 2;

B.barrier();

```

```

Thread 2:

B.barrier();

var = *x + *y;

```

What is this guaranteed to be?

```

Thread 0:

*x = 1;

B.barrier();

```

```

Thread 1:

*y = 2;

B.barrier();

```

sometimes called a phase

extending to the next barrier leave

Barrier Interval 0 Barrier Interval 1 thread 0 barrier arrive barrier leave thread 1 \*y = 2 barrier arrive

barrier arrive thread 2 barrier leave var = \*x + \*v

barrier leave

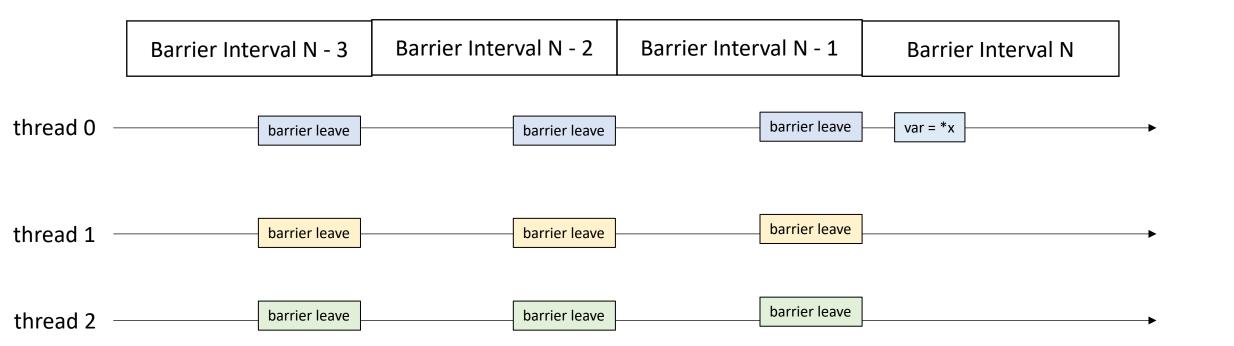

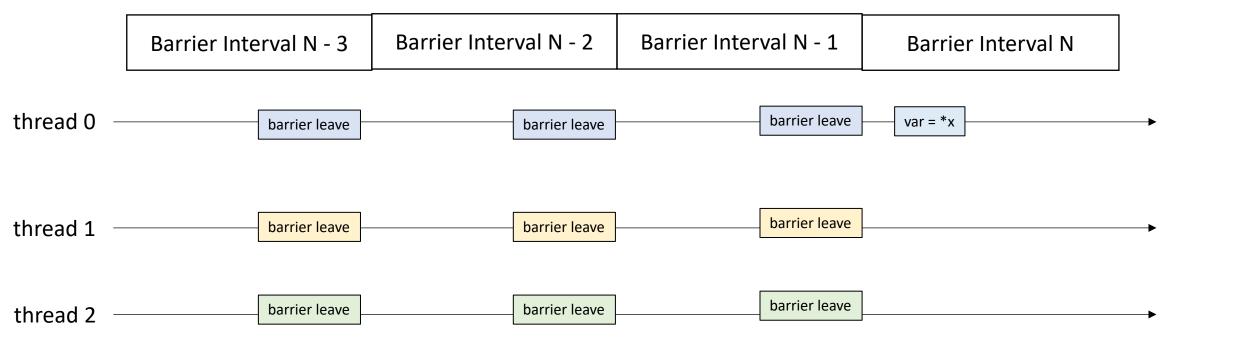

- Barrier Property:

- If the only concurrent object you use in your program is a barrier (no mutexes, concurrent data-structures, atomic accesses)

- If every barrier interval contains no data conflicts, then

your program will be deterministic (only 1 outcome allowed)

• much easier to reason about ©

Assume we are reading from x

We are only allowed to return one possible value

no data conflicts means that x is written to at most once per barrier interval

Assume we are reading from x

We are only allowed to return one possible value

Assume we are reading no data conflicts means that x is written to at most once from x per barrier interval We are only allowed to return one possible not allowed value Barrier Interval N - 2 Barrier Interval N - 1 Barrier Interval N - 3 Barrier Interval N thread 0 barrier leave barrier leave var = \*x\*x = 2barrier leave barrier leave thread 1 barrier leave barrier leave \*x = 1 barrier leave barrier leave barrier leave thread 2

Assume we are reading no data conflicts means that x is written to at most once from x per barrier interval We are only allowed to we will read from the write return one possible from the most recent barrier interval value Barrier Interval N - 2 Barrier Interval N - 3 Barrier Interval N - 1 Barrier Interval N thread 0 barrier leave \*x = 2barrier leave var = \*xbarrier leave barrier leave \*x = 1thread 1 barrier leave barrier leave barrier leave barrier leave barrier leave thread 2

## Schedule

• Module 4 introduction

- Barriers

- Specification

- Implementation

First attempt at implementation

```

class Barrier {

private:

atomic int counter;

int num threads;

public:

Barrier(int num threads) {

counter = 0;

this->num_threads = num_threads;

void barrier() {

// ??

```

```

class Barrier {

private:

atomic int counter;

int num threads;

public:

Barrier(int num_threads) {

counter = 0;

this->num threads = num threads;

void barrier() {

int arrival_num = atomic_fetch_add(&counter, 1);

// What next?

```

First handle the case where the thread is the last thread to arrive

```

class Barrier {

private:

atomic int counter;

int num threads;

public:

Barrier(int num threads) {

counter = 0;

this->num threads = num threads;

void barrier() {

int arrival num = atomic fetch add(&counter, 1);

if (arrival_num == num_threads - 1) {

counter.store(0);

// What next?

```

Spin while there is a thread waiting at the barrier

```

class Barrier {

private:

atomic int counter;

int num threads;

public:

Barrier(int num threads) {

counter = 0;

this->num threads = num threads;

void barrier() {

int arrival num = atomic fetch add(&counter, 1);

if (arrival_num == num_threads - 1) {

counter.store(0);

else {

while (counter.load() != 0);

```

Spin while there is a thread waiting at the barrier

Does this work?

```

class Barrier {

private:

atomic int counter;

int num threads;

public:

Barrier(int num threads) {

counter = 0;

this->num threads = num threads;

void barrier() {

int arrival num = atomic fetch add(&counter, 1);

if (arrival_num == num_threads - 1) {

counter.store(0);

else {

while (counter.load() != 0);

```

```

Thread 0:

```

B.barrier();

B.barrier();

```

void barrier() {

int arrival_num = atomic_fetch_add(&counter, 1);

if (arrival_num == num_threads) {

counter.store(0);

}

else {

while (counter.load() != 0);

}

}

```

### Thread 1:

B.barrier();

B.barrier();

thread 0

#### num\_threads == 2

#### Thread 0:

B.barrier();

B.barrier();

```

void barrier() {

int arrival_num = atomic_fetch_add(&counter, 1);

if (arrival_num == num_threads - 1) {

counter.store(0);

}

else {

while (counter.load() != 0);

}

}

```

### Thread 1:

B.barrier();

B.barrier();

arrival\_num = 1

arrival\_num = 0

thread 0

```

num_threads == 2

counter == 2

```

### Thread 0:

B.barrier();

B.barrier();

```

void barrier() {

int arrival_num = atomic_fetch_add(&counter, 1);

if (arrival_num == num_threads - 1) {

counter.store(0);

}

else {

while (counter.load() != 0);

}

}

```

### Thread 1:

B.barrier();

B.barrier();

arrival\_num = 1

arrival\_num = 0

thread 0

```

num_threads == 2

counter == 0

```

### Thread 0:

B.barrier();

B.barrier();

```

void barrier() {

int arrival_num = atomic_fetch_add(&counter, 1);

if (arrival_num == num_threads - 1) {

counter.store(0);

}

else {

while (counter.load() != 0);

}

}

```

### Thread 1:

B.barrier();

B.barrier();

arrival\_num = 1

arrival\_num = 0

thread 0

```

num_threads == 2

counter == 0

```

```

Thread 0:

```

B.barrier();

B.barrier();

```

void barrier() {

int arrival_num = atomic_fetch_add(&counter, 1);

if (arrival_num == num_threads - 1) {

counter.store(0);

}

else {

while (counter.load() != 0);

}

}

```

#### Thread 1:

B.barrier();

B.barrier();

Leaves barrier

arrival num = 0

in a perfect world, thread 1 executes now and leaves the barrier

thread 0

```

num_threads == 2

counter == 0

```

```

Thread 0:

```

B.barrier();

B.barrier();

```

void barrier() {

int arrival_num = atomic_fetch_add(&counter, 1);

if (arrival_num == num_threads - 1) {

counter.store(0);

}

else {

while (counter.load() != 0);

}

}

```

#### Thread 1:

B.barrier();

B.barrier();

Leaves barrier

arrival num = 0

in a perfect world, thread 1 executes now and leaves the barrier

but what if the OS preempted thread 1? Or it was asleep?

```

num_threads == 2

counter == 0

```

```

Thread 0:

```

B.barrier();

```

void barrier() {

int arrival_num = atomic_fetch_add(&counter, 1);

if (arrival_num == num_threads - 1) {

counter.store(0);

}

else {

while (counter.load() != 0);

}

}

```

#### Thread 1:

B.barrier();

B.barrier();

enters next barrier

arrival num = 0

in a perfect world, thread 1 executes now and leaves the barrier

but what if the OS preempted thread 1? Or it was asleep?

```

num_threads == 2

counter == 1

```

```

Thread 0:

```

B.barrier();

```

void barrier() {

int arrival_num = atomic_fetch_add(&counter, 1);

if (arrival_num == num_threads - 1) {

counter.store(0);

}

else {

while (counter.load() != 0);

}

}

```

#### Thread 1:

B.barrier();

B.barrier();

arrival\_num == 0

arrival num = 0

in a perfect world, thread 1 executes now and leaves the barrier

but what if the OS preempted thread 1? Or it was asleep?

```

num_threads == 2

counter == 1

```

```

Thread 0:

```

B.barrier();

```

arrival_num == 0

```

```

void barrier() {

int arrival_num = atomic_fetch_add(&counter, 1);

if (arrival_num == num_threads - 1) {

counter.store(0);

}

else {

while (counter.load() != 0);

}

}

```

### Thread 1:

B.barrier();

B.barrier();

Thread 1 wakes up! Doesn't think its missed anything

arrival num = 0

in a perfect world, thread 1 executes now and leaves the barrier

```

num_threads == 2

counter == 1

```

```

Thread 0:

```

B.barrier();

arrival\_num == 0

```

void barrier() {

int arrival_num = atomic_fetch_add(&counter, 1);

if (arrival_num == num_threads - 1) {

counter.store(0);

}

else {

while (counter.load() != 0);

}

}

```

### Thread 1:

B.barrier();

B.barrier();

Thread 1 wakes up! Doesn't think its missed anything

arrival num = 0

in a perfect world, thread 1 executes now and leaves the barrier

Both threads get stuck here!

B.barrier();

B.barrier();

```

void barrier() {

int arrival_num = atomic_fetch_add(&counter, 1);

if (arrival_num == num_threads - 1) {

counter.store(0);

}

else {

while (counter.load() != 0);

}

}

```

## Thread 1:

B.barrier();

B.barrier();

Ideas for fixing?

```

B.barrier();

B.barrier();

```

```

void barrier() {

int arrival_num = atomic_fetch_add(&counter, 1);

if (arrival_num == num_threads - 1) {

counter.store(0);

}

else {

while (counter.load() != 0);

}

}

```

# Thread 1:

```

B.barrier();

B.barrier();

```

Ideas for fixing?

Two different barriers that alternate?

```

B0.barrier();

B1.barrier();

```

```

void barrier() {

int arrival_num = atomic_fetch_add(&counter, 1);

if (arrival_num == num_threads - 1) {

counter.store(0);

}

else {

while (counter.load() != 0);

}

}

```

# Ideas for fixing?

Two different barriers that alternate?

Pros: simple to implement

Cons: user has to alternate barriers

#### Thread 1:

```

B0.barrier();

B1.barrier();

```

```

B0.barrier();

B1.barrier();

```

```

void barrier() {

int arrival_num = atomic_fetch_add(&counter, 1);

if (arrival_num == num_threads - 1) {

counter.store(0);

}

else {

while (counter.load() != 0);

}

}

```

#### Thread 1:

```

B0.barrier();

B1.barrier();

```

Ideas for fixing?

Two different barriers that alternate?

Pros: simple to implement

Cons: user has to alternate barriers

```

B.barrier();

if (...) {

B.barrier();

}

B.barrier();

```

How to alternate these calls?

# Sense Reversing Barrier

Book Chapter 17

Alternating "sense" dynamically

```

Thread 0:

B.barrier();

B.barrier();

```

```

sync on sense = false

```

```

Thread 1:

B.barrier();

B.barrier();

```

# Sense Reversing Barrier

Book Chapter 17

Alternating "sense" dynamically

```

Thread 0:

B.barrier();

B.barrier();

```

```

sync on sense = true

```

```

Thread 1:

B.barrier();

B.barrier();

```

```

class SenseBarrier {

private:

atomic int counter;

int num threads;

atomic bool sense;

bool thread sense[num threads];

public:

Barrier(int num threads) {

counter = 0;

this->num threads = num threads;

sense = false;

thread sense = {true, ...};

void barrier(int tid) {

int arrival num = atomic fetch add(&counter, 1);

if (arrival num == num threads) {

counter.store(0);

sense = thread sense[tid];

else {

while (sense != thread sense[tid]);

thread sense[tid] = !thread sense[tid];

```

thread sense = true

```

num_threads == 2

counter == 0

sense = false

```

thread\_sense = true

```

Thread 0:

B.barrier();

B.barrier();

```

```

void barrier(int tid) {

int arrival_num = atomic_fetch_add(&counter, 1);

if (arrival_num == num_threads-1) {

counter.store(0);

sense = thread_sense[tid];

}

else {

while (sense != thread_sense[tid]);

}

thread_sense[tid] = !thread_sense[tid];

}

```

```

Thread 1:

B.barrier();

B.barrier();

```

```

thread_sense = true

arrival_num = 1

```

```

Thread 0:

B.barrier();

B.barrier();

```

```

num_threads == 2

counter == 2

sense = false

void barrier(int tid) {

int arrival_num = atomic_fetch_add(&counter, 1);

if (arrival_num == num_threads-1) {

counter.store(0);

sense = thread_sense[tid];

}

else {

while (sense != thread_sense[tid]);

}

thread_sense[tid] = !thread_sense[tid];

```

```

thread_sense = true

arrival_num = 0

```

```

Thread 1:

B.barrier();

B.barrier();

```

```

thread_sense = true

arrival_num = 1

```

```

Thread 0:

B.barrier();

B.barrier();

```

```

num_threads == 2

counter == 2

sense = false

void barrier(int tid) {

int arrival_num = atomic_fetch_add(&counter, 1);

if (arrival_num == num_threads-1) {

counter.store(0);

sense = thread_sense[tid];

}

else {

while (sense != thread_sense[tid]);

}

thread_sense[tid] = !thread_sense[tid];

}

```

```

thread_sense = true

arrival_num = 0

```

```

Thread 1:

B.barrier();

B.barrier();

```

```

thread_sense = false

arrival_num = 1

```

```

Thread 0:

B.barrier();

B.barrier();

```

```

thread_sense = true

arrival_num = 0

```

```

Thread 1:

B.barrier();

B.barrier();

```

```

thread_sense = false

arrival_num = ?

```

```

Thread 0:

B.barrier();

B.barrier();

```

```

num_threads == 2

counter == 0

sense = true

void barrier(int tid) {

int arrival_num = atomic_fetch_add(&counter, 1);

if (arrival_num == num_threads-1) {

counter.store(0);

sense = thread_sense[tid];

}

else {

while (sense != thread_sense[tid]);

}

thread sense[tid] = !thread_sense[tid];

}

```

```

thread_sense = true

arrival_num = 0

```

```

Thread 1:

B.barrier();

B.barrier();

```

Remember the issue! Thread 1 went to sleep around this time and thread 0 went into the barrier again!

```

thread_sense = false

arrival_num = 0

```

```

Thread 0:

B.barrier();

B.barrier();

```

```

thread_sense = true

arrival_num = 0

```

```

Thread 1:

B.barrier();

```

```

thread_sense = false

arrival_num = 0

```

```

Thread 0:

B.barrier();

B.barrier();

```

```

thread_sense = true

arrival_num = 0

```

```

Thread 1:

B.barrier();

B.barrier();

```

both are waiting!, but thread 1 can leave

```

thread_sense = false

arrival_num = 0

```

```

Thread 0:

B.barrier();

B.barrier();

```

```

thread_sense = false

arrival_num = 0

```

```

Thread 1:

B.barrier();

B.barrier();

```

both are waiting!, but thread 1 can leave

```

thread_sense = false

arrival_num = 0

```

```

Thread 0:

B.barrier();

B.barrier();

```

```

num_threads == 2

counter == 1

sense = true

void barrier(int tid) {

int arrival_num = atomic_fetch_add(&counter, 1);

if (arrival_num == num_threads-1) {

counter.store(0);

sense = thread_sense[tid];

}

else {

while (sense != thread_sense[tid]);

}

thread_sense[tid] = !thread_sense[tid];

}

```

```

thread_sense = false

arrival_num = ?

Thread 1:

B.barrier();

B.barrier();

```

Thread 1 finishes the barrier

```

thread_sense = false

arrival_num = 0

```

```

Thread 0:

B.barrier();

B.barrier();

```

```

num_threads == 2

counter == 1

sense = true

void barrier(int tid) {

int arrival_num = atomic_fetch_add(&counter, 1);

if (arrival_num == num_threads-1) {

counter.store(0);

sense = thread_sense[tid];

}

else {

while (sense != thread_sense[tid]);

}

thread_sense[tid] = !thread_sense[tid];

```

```

thread_sense = false

arrival_num = ?

<u>Thread 1:</u>

B.barrier();

B.barrier();

```

```

thread_sense = false

arrival_num = 0

```

```

Thread 0:

B.barrier();

B.barrier();

```

```

thread_sense = false

arrival_num = 1

<u>Thread 1:</u>

B.barrier();

```

```

thread_sense = false

arrival_num = 0

```

```

Thread 0:

B.barrier();

B.barrier();

```

```

num_threads == 2

counter == 2

sense = true

void barrier(int tid) {

int arrival_num = atomic_fetch_add(&counter, 1);

if (arrival_num == num_threads-1) {

counter.store(0);

sense = thread_sense[tid];

}

else {

while (sense != thread_sense[tid]);

}

thread_sense[tid] = !thread_sense[tid];

}

```

```

thread_sense = false

arrival_num = 1

<u>Thread 1:</u>

B.barrier();

```

```

thread_sense = false

arrival_num = 0

```

```

Thread 0:

B.barrier();

B.barrier();

```

```

num_threads == 2

counter == 0

sense = false

void barrier(int tid) {

int arrival_num = atomic_fetch_add(&counter, 1);

if (arrival_num == num_threads-1) {

counter.store(0);

sense = thread_sense[tid];

}

else {

while (sense != thread_sense[tid]);

}

thread_sense[tid] = !thread_sense[tid];

}

```

```

thread_sense = false

arrival_num = 1

<u>Thread 1:</u>

B.barrier();

```

```

thread_sense = false

arrival_num = 0

```

```

Thread 0:

B.barrier();

B.barrier();

```

```

num_threads == 2

counter == 0

sense = false

void barrier(int tid) {

int arrival_num = atomic_fetch_add(&counter, 1);

if (arrival_num == num_threads-1) {

counter.store(0);

sense = thread_sense[tid];

}

else {

while (sense != thread_sense[tid]);

}

thread_sense[tid] = !thread_sense[tid];

```

```

thread_sense = false

arrival_num = 1

Thread 1:

```

```

Thread 1:

B.barrier();

B.barrier();

```

thread 0 can leave, thread 1 can leave and the barrier works as expected!

# See you on Wednesday!

• Starting on module 4

• Work on HW 3